‘xD’에 대한 검색결과 74 건 입니다

알림·뉴스 ( 34 건)

-

‘22년 상반기 및 6월 주요유통업체 매출동향 2022-07-28

8px; height: 188px;" alt="그림입니다. 원본 그림의 이름: CLP000021c80225.bmp 원본 그림의 크기: 가로 278pixel, 세로 251pixel" src="https://www.motie.go.kr/ekpImg/000009/20220728111238430_6XD25PPI.jpg" />

1. 전체 매출 동향 □ (전체 매출) '22년 상반기 주요 유통업체 매출은 오프라인(8.4%) 부문과 온라인(10.3%) 부문이 모두 성장세를 유지하며, 전년 대비 9.3% 증가 ㅇ ...

1. 전체 매출 동향 □ (전체 매출) '22년 상반기 주요 유통업체 매출은 오프라인(8.4%) 부문과 온라인(10.3%) 부문이 모두 성장세를 유지하며, 전년 대비 9.3% 증가 ㅇ ...>알림·뉴스>보도자료>보도·참고자료

-

0728(29조간)유통물류과, '22년 상반기 및 6월 주요유통업체 매출동향.pdf

미리보기

미리보기

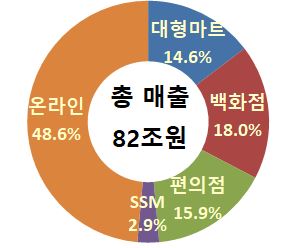

문화체육관광부 보 도 자 료 보도 일시 2022. 7. 28.(목) 11:00 < 7.29.(금) 조간 > 배포 일시 2022. 7. 28.(목) 담당 부서 중견기업정책관 책임자 과 장 정상용(044-203-4380) 유통물류과 담당자 사무관 박진현(044-203-4385) ‘22년 상반기 및 6월 주요유통업체 매출동향 - ’22. 7. 28.(목) 배포 - < 일 러 두 기 > 1. 본 동향은 소비동향 파악을 목적으로 주요 온ㆍ오프라인 유통업체의 월간 매출액을 조사‧분석한 자료임 2. 오프라인 유통업체 매출동향은 전체 유통업체가 아닌 주요 오프라인 유통업체 13개사의 월간 매출액을 조사‧분석한 결과임 3. 온라인 유통업체 매출동향은 온라인 유통업체 12개사의 월간 거래액을 조사‧분석한 결과로, 통계청의 승인을 받지 않은 자료임 4. 본 동향은 통계청의 「서비스업동향조사」‧「온라인쇼핑 동향조사」와는 모집단, 작성항목 등이 달라 자료간 증감 크기나 방향이 상이할 수 있음 ‘22년 상반기 주요 유통업체 매출, 전년 대비 9.3% 증가 - 오프라인 유통업체 8.4% 증가, 온라인 유통업체 10.3% 증가 - ‘22년 6월 주요 유통업체 매출, 전년동월 대비 9.2% 증가 - 오프라인 유통업체 9.3% 증가, 온라인 유통업체 9.1% 증가 - Ⅰ 2022년 상반기 매출동향 [반기] <’18~‘22년 상반기 전년 대비 매출 증감률(%) 추이> <‘21년 및 ’22년 상반기 업태별 매출 구성비(%)> ‘21년 상반기 업태별 매출구성비 ‘22년 상반기 업태별 매출구성비 1. 전체 매출 동향 □ (전체 매출) '22년 상반기 주요 유통업체 매출은 오프라인(8.4%) 부문과 온라인(10.3%) 부문이 모두 성장세를 유지하며, 전년 대비 9.3% 증가 ㅇ (오프라인, 8.4%) 지난해 코로나19 영향에 대한 기저효과와 거리두기 완화에 따라 백화점(18.4%)을 중심으로 매출이 증가 ㅇ (온라인, 10.3%) 온라인을 통한 화장품구매, 장보기 등 온라인ㆍ비대면 소비 문화의 확산이 이어져 매출이 두 자릿수 성장 <‘21년 상반기 vs. ’22년 상반기 매출 비중 및 매출 증감률> 구분 ‘21년 상반기 ‘22년 상반기 매출 비중 매출 증감률 매출 비중 매출 증감률 대형마트 16.3% 0.3% 14.6% △1.5% 백 화 점 16.6% 26.2% 18.0% 18.4% 편 의 점 15.8% 6.2% 15.9% 10.1% S S M 3.2% △10.0% 2.9% △1.9% 오프라인 합계 51.9% 8.6% 51.4% 8.4% 온라인 합계 48.1% 16.1% 48.6% 10.3% 전체 100.0% 12.1% 100.0% 9.3% □ (상품군별 매출비중) 해외여행에 대한 제약이 지속되면서 유명브랜드 (0.8%p)의 매출비중이 증가하고, 온라인을 통한 음식배달ㆍe-쿠폰 사용 등이 늘어 서비스/기타(0.6%p) 상품군의 비중도 증가 ㅇ 지난해 코로나19의 영향으로 매출이 늘었던 가전/문화(△0.9%p), 생활/ 가정(△0.5%p) 등 다른 상품군의 비중은 감소 <’21년 vs. ‘22년 상반기 상품군별 매출구성비(%)> 2. 유통업체별 매출 동향 오프라인 유통업체 □ 지난해 코로나19 영향에 대한 기저효과와 거리두기 완화로 백화점(18.4%) 매출이 큰 폭으로 성장하고 편의점(10.1%)의 매출도 늘어, 대형마트(△1.5%)ㆍSSM (△1.9%)의 매출 감소에도 전체 오프라인 매출은 8.4% 증가 ㅇ (대형마트) 가정/생활(△3.7%), 가전/문화(△3.6%) 등 매출 감소로 카페 및 푸드코트 등 기타(3.7%), 의류(0.6%)의 매출 회복이 있었으나, 전체 매출 (△1.5%) 소폭 감소 ㅇ (백화점) 유명브랜드(26.9%), 아동/스포츠(26.3%), 여성의류(정장 17.1%, 캐주얼16.1%), 남성의류(19.8%) 등 전 상품군의 매출이 호조세를 이어가 전체 매출(18.4%) 크게 증가 ㅇ (편의점) 근거리ㆍ소량구매 선호에 따라 가공‧즉석 등 식품군(10.6%)의 매출이 늘고 생활용품(11.5%)의 매출도 증가해 전체 매출(10.1%) 증가 ㅇ (준대규모점포(SSM)) 온라인으로 구매채널이 이동한 일상용품(△4.9%)‧ 생활잡화(△1.1%) 등 비식품군(△3.3%)과 식품군(△1.7%) 매출이 모두 감소하여 전체 매출(△1.9%) 감소 <’22년 상반기 오프라인 업태별 전년 대비 매출 증감률 (단위: %)> 구분 전체 대형마트 백화점 편의점 SSM 매출 증감률 8.4 △1.5 18.4 10.1 △1.9 온라인 유통업체 □ 온라인을 통한 장보기 등의 보편화로 식품(17.8%) 분야 매출이 증가하며 전체 온라인 매출 10.3% 증가 ㅇ 야외활동 재개에 따른 화장품(21.2%), 음식배달ㆍ공연티켓 등의 서비스/ 기타(17.0%) 매출이 가파르게 성장 Ⅰ 2022년 6월 매출동향 [월간] <‘22년 6월 기준 전년동월 대비 매출 증감률(%)> 온‧오프라인 매출 증감률 오프라인 업태별 매출 증감률 1. 전체 매출 동향 □ (전체 매출) 오프라인 부문(9.3%)과 온라인 부문(9.1%)이 고른 성장세를 보이며, 전체 매출은 전년동월 대비 9.2% 상승 ㅇ (오프라인) 거리두기 완화 등 야외활동 증가와 보복소비 영향으로 아동/ 스포츠(24.1%)를 비롯, 모든 품목에서 매출 상승 ㅇ (온라인) 실외활동과 모임 증가로 화장품・식품 등 온라인 구매와 서비스 (공연·레저 상품 예약) 수요가 지속되며 전 품목에서 매출 상승 * 오프라인/온라인 매출규모(조원) : (‘22.4월) 7.01 / 6.59 ⇒ (‘22.5월) 7.48 / 6.97 ⇒ (’22.6월) 7.08 / 6.50 <주요 유통업체의 전년동월 대비 월별 매출 증감률 (단위 : %)> 구분 ‘21년 ‘22년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 전체 11.4 13.1 6.4 8.2 14.4 9.6 11.6 13.9 4.7 7.1 10.6 10.1 9.2 오프라인 4.8 7.0 2.5 3.3 10 4.6 10.3 18.4 △3.8 6.3 10.2 9.3 9.3 온라인 19.6 20.2 11.1 14.5 19.7 14.8 12.8 9.1 14.2 7.9 11.0 11.0 9.1 □ (상품군별 매출) 해외유명브랜드(19.6%), 패션/잡화(11.7%), 서비스/기타 (10.8%), 아동/스포츠(9.2%) 등 전체 상품군 매출 상승 ㅇ (오프라인) 아동/스포츠(24.1%), 해외유명브랜드(19.6%)와 패션/잡화 (13.9%) 분야가 큰 폭으로 상승하면서 전체 상품군에서 매출 상승 ㅇ (온라인) 식품(17.9%), 서비스/기타(13.6%), 패션/잡화(9.6%) 등 판매 호조세가 이어지면서 전체 상품군에서 매출 상승 <’22년 6월 전년동월 대비 상품군별 매출 증감률 (단위 : %)> 구분 전체 가전/ 문화 패션/ 잡화 아동/ 스포츠 식품 생활/ 가정 서비스/ 기타 해외유명 브랜드 전체 (비중,%) 9.2 (100) 0.8 (12.1) 11.7 (13.7) 9.2 (5.8) 9.5 (34.5) 7.7 (12.6) 10.8 (15.2) 19.6 (6.1) 오프라인 9.3 1.0 13.9 24.1 5.6 7.3 8.0 19.6 온라인 9.1 0.8 9.6 0.7 17.9 8.0 13.6 - □ (구매건수ㆍ구매단가) 백화점·편의점 방문객 증가, 대형마트·SSM 방문객 감소 추세가 지속(`22.4월~6월), 전체 구매건수(4.3%) 증가와 함께 농·축산물 등 물가상승 영향으로 전체 구매단가(4.7%)도 증가 <’22년 6월 오프라인 부문 구매건수ㆍ단가 증감률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 구매건수 4.3 △2.9 9.8 5.5 △4.4 구매단가 4.7 5.3 7.7 3.0 2.3 * 온라인은 구매건수를 집계하지 않고 있어 통계자료에 미포함 □ (업태별 매출 비중) 전년 동월 대비 오프라인·온라인 매출 비중은 유사 ㅇ 오프라인 업태 중 백화점(1.4%p)의 매출 비중은 늘고, 대형마트(△0.9%p)·SSM (△0.3%p)은 감소, 편의점은 변동 없음 <’21년 vs. ’22년 6월 업태별 매출구성비> ’21년 6월 업태별 매출구성비 ’22년 6월 업태별 매출구성비 2. 유통업체별 매출 동향 오프라인 유통업체 □ 대형마트(2.3%)ㆍ백화점(18.2%)ㆍ편의점(8.6%)의 매출은 증가하고, SSM (△2.2%)의 매출은 감소하였으며 전체 매출은 9.3% 증가 ㅇ (대형마트) 거리두기 완화에 따른 야외활동 증가 등으로 의류(5.3%), 잡화(2.3%) 등 전 품목에서 소폭 성장하면서 전체 매출은 2.3% 증가 ㅇ (백화점) 방문객수 증가(구매건수 9.8%) 추세가 지속되었고, 전 품목 에서 판매호조(아동/스포츠 27.4%, 남성의류 18.7%, 여성정장 17.8% 등)를 보이며 전체 매출은 18.2% 증가 ㅇ (편의점) 정상 등교·근무 등으로 이용객수가 늘며, 생활용품(19.9%), 잡화 (11.6%), 가공식품(10.0%) 등 전 품목 판매호조로 전체 매출 8.6% 증가 ㅇ (준대규모점포) 가공식품(3.6%)을 제외한 일상용품(△6.9%), 농·수축산 (△5.1%) 등 대부분 품목의 판매 부진으로 전체 매출은 2.2% 감소 <’22년 6월 오프라인 업태별 전년동월 대비 매출 증감률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 매출 증감률 9.3 2.3 18.2 8.6 △2.2 □ (점포당 매출) 점포수는 대형마트·SSM은 감소, 백화점·편의점은 증가 하였으며, 점포당 매출은 SSM을 제외한 대부분 업태에서 증가 <’22년 6월 전년동월 대비 점포당 매출 및 점포수 증강률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 점포당 매출 증감률 13.0 4.7 14.2 1.3 △1.1 점포 수 증감률 6.9 △2.3 3.4 7.2 △1.1 온라인 유통업체 □ 온라인 유통업체 매출은 전년동월 대비 9.1% 증가하였으며, 도서/문구 (△2.3%), 스포츠(△0.5%) 품목을 제외한 대부분 품목에서 매출이 상승 ㅇ 모임·실외활동 증가에 따른 화장품(18.1%) 및 가공식품·식음료 등 식품(17.9%) 수요증가, 여행·공연 예약상품 등 서비스/기타(13.6%) 품목의 판매호조 지속 <‘22년 6월 상품군별 전년동월 대비 매출증감률‧매출비중 (단위 : %)> 구분 전체 가전 전자 도서 문구 패션 의류 스포츠 화장품 아동 유아 식품 생활 가구 서비스 기타 매출증감률 9.1 1.0 △2.3 6.0 △0.5 18.1 2.1 17.9 8.0 13.6 매출비중 100.0 20.5 1.7 9.9 3.7 4.7 3.4 24.2 15.5 16.4 참고 조사대상 및 유사통계 간 비교 【 (참고1) 매출동향 조사대상 】 □ 오프라인 유통업체(13개사) ∙ 백화점(3) : 롯데백화점, 현대백화점, 신세계백화점 ∙ 대형마트(3) : 이마트, 홈플러스, 롯데마트 ∙ 편의점(3) : 지에스25, 씨유, 세븐일레븐(바이더웨이 포함) ∙ 준대규모점포(SSM)(4) : 이마트에브리데이, 롯데슈퍼, 지에스더후레쉬, 홈플러스익스프레스 □ 온라인 유통업체(12개사) ∙ G마켓글로벌(G마켓‧옥션), 11번가, 인터파크, 쿠팡, SSG(이마트‧신세계), 에이케이몰, 홈플러스, 갤러리아몰, 롯데마트, 롯데온, 위메프, 티몬 ※ 유통업체별 협회(백화점·체인스토어·온라인쇼핑협회) 및 개별 유통업체(편의점)를 통해 조사 【 (참고2) 유사통계 간 비교 】 통계 명 주요 유통업체 (오프라인) 매출동향조사 서비스업동향조사 온라인쇼핑동향조사 작성기관 산업통상자원부 통계청 작성목적 소비동향 파악 서비스업‧도소매업 사업체의 경영실태 파악 온라인쇼핑동향 분석 모집단 주요 오프라인 유통업체 (13개사) 국내에서 서비스업을 운영하는 사업체 전체 연간거래액이 24백만원 이상인 온라인쇼핑 운영업체 (13,000여개) 표본추출틀 주요 오프라인 유통업체 (13개사) 2015 경제총조사 결과, 한국표준산업분류 대분류 13개 업종 공정위 PG사, 새올 행정시스템, 경총자료 조사대상 주요 오프라인 유통업체 13개사 (유의표본) 표본 17,300개 사업체 표본 1,100개 사업체 포괄범위 상품 및 서비스 거래금액 판매액(상품) 23개 상품군별 상품 및 서비스 거래금액 붙임 조사대상 유통업체별 매출 추이 □ 대형마트 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비 식품 식품 합계 가전/문화 의류 가정/생활 스포츠 잡화 기타 소계 ‘21. 6월 △15.2 △10.4 △15.3 △8.4 △29.4 0.0 △14.6 6.0 △2.4 7월 15.0 △3.5 △7.4 11.8 △4.1 △1.5 1.3 10.9 7.3 8월 △14.9 △19.1 △16.1 △13.6 △33.2 △10.8 △16.5 0.4 △5.5 9월 △5.5 △1.1 △14 5.1 △14.4 8.1 △8.6 △15.3 △13.3 10월 9.6 △1.5 △6.8 △10.4 △21.2 △5.4 △1.8 3.5 1.4 11월 △17.8 △1.8 △14.8 △13.7 △17.2 0.1 △13.6 △8.3 △10.3 12월 △6.1 7.9 △7.7 5.2 6.3 30.1 △2.3 △7.9 △6.1 ‘22. 1월 △2.7 13.1 13.5 6.4 10.6 16.9 6.8 16.9 13.8 2월 0.5 △20.5 △24.1 △13.3 △20.5 △7.1 △14.6 △28.7 △24.0 3월 △8.0 △17.8 △5.3 △13.9 △16.1 △4.4 △9.0 4.8 0.0 4월 △0.6 13.2 △2.7 1.8 10.8 5.3 1.3 2.3 2.0 5월 △9.7 9.0 △3.9 5.3 6.0 3.0 △3.1 △3.2 △3.0 6월 1.0 5.3 1.1 1.4 2.3 8.2 1.8 2.3 2.3 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) ㅇ 상품군별 매출 비중 (단위 : %) 구분 비 식품 식품 합계 가전/문화 의류 가정/생활 스포츠 잡화 기타 소계 ‘22. 2월 14.0 3.4 14.0 1.3 1.6 2.0 36.4 63.6 100 ‘22. 3월 11.0 3.5 12.7 1.3 1.8 2.1 32.4 67.6 100 ‘22. 4월 10.7 4.9 12.4 1.7 2.3 2.2 34.2 65.8 100 ‘22. 5월 11.7 5.3 13.0 2.0 2.5 2.4 36.9 63.1 100 ‘22. 6월 10.8 4.8 14.1 1.8 2.3 2.4 36.2 63.8 100 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 △1.8 △1.3 △11.5 △16.1 △9.7△11.5 △7.3 2.9 △13.1 △2.8 △4.1 △5.0 △2.9 구매단가 △0.6 8.7 6.8 3.4 12.4 1.3 1.3 10.6 △12.5 2.9 6.4 2.1 5.3 점포당 매출 0.9 11.2 △5.5 △10.8 4.1 △7.5 △3.2 17.4 △22.2 5.5 3.9 △1.5 4.7 * '22.6월 1인당 구매단가 : 52,041원 (전년동월 49,406원) ** '22.6월 점포당 매출액 : 49.6억원 (전년동월 47.4억원) / ‘22.6월 점포 수 : 381개 2019년 연 간 2020년 연 간 2021년 연 간 2022년 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 △8.1 △4.0 △5.1 △5.8 △5.5 △0.7 0.1 △3.0 0.4 0.2 △4.7 △5 △2.3 △3.2 0.3 □ 백화점 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비식품품목 식품 합계 잡 화 여성 정장 여성 캐주얼 남성 의류 아동 스포츠 가정 용품 해외유명 브랜드 소계 ‘21. 6월 △5.4 4.1 4.1 4.9 17.0 △0.5 31.5 12.9 10.8 12.8 7월 △9.2 △9.5 0.9 △0.6 16.5 16.5 18.8 9.5 △2.6 7.8 8월 △2.6 1.5 △6.8 4.5 24.8 25.6 18.6 14.3 4.5 13 9월 12.5 19.3 23.6 27 36.9 17.4 38.1 27.3 11.8 24.3 10월 5.0 7.7 5.4 12.8 19.6 22.2 39.4 21.5 16.9 21 11월 7.3 15 13.3 14.9 25.7 3 32.9 18.9 13.1 18.3 12월 30.6 36.1 48.6 40.5 55.3 14.6 42.8 37.7 28.3 36.5 ‘22. 1월 31.0 23.7 35.5 38.7 46.3 6.9 46.5 32.7 60.0 37.2 2월 3.2 13.8 1.9 10.8 11.9 9.3 32.5 17.4 △30.3 9.3 3월 △2.4 6.9 △2.7 3.8 12.6 △5.4 21.1 8.7 0.2 7.8 4월 14.7 19.2 22.2 21.2 33.4 6.8 22.5 20.0 10.4 19.1 5월 21.9 22.7 25.3 24.5 30.0 3.1 23.6 20.8 12.4 19.9 6월 14.4 17.8 17.3 18.7 27.4 10.6 19.6 18.1 16.2 18.2 * 자료 : 해외유명브랜드는 각사 분류 기준 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 1.0 △1.7 △0.2 △0.1 △19.9 △8.4 △5.0 △6.0 △9.8 31.2 21.5 14.6 24.8 24.1 17.6 19.1 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비식품품목 식품 합계 잡 화 여성 정장 여성 캐주얼 남성 의류 아동 스포츠 가정 용품 해외유명 브랜드 소계 ’22. 2월 9.7 6.7 5.3 3.4 10.3 16.4 37.3 89.2 10.8 100 ’22. 3월 9.4 8.2 6.2 4.1 11.5 13.4 36.4 89.1 10.9 100 ‘22. 4월 10.3 7.0 6.7 4.6 12.8 13.1 34.9 89.4 10.6 100 ‘22. 5월 12.0 6.8 6.8 4.5 12.4 13.2 33.4 89.0 11.0 100 ‘22. 6월 11.7 6.5 7.4 4.2 11.8 13.5 33.5 88.6 11.4 100 * 자료 : 해외유명브랜드는 각사 분류 기준 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 1.4 △8.1 △6.8 13 7.1 7.5 29.6 21.2 △1.5 △7.2 7.8 11.4 9.8 구매단가 11.2 17.3 21.2 10 13 10.1 5.3 13.3 10.9 16.1 10.4 7.6 7.7 점포당 매출 10.8 5.9 9.2 18.1 15 12.4 29.7 30.4 5.6 4.2 15.1 15.9 14.2 * '22.6월 1인당 구매단가 : 114,201원 (전년동월 106,057원) ** '22.6월 점포당 매출액 : 413.3억원 (전년동월 361.8억원) / ‘22.6월 점포 수 : 60개 □ 편의점 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비 식품품목 식품 합계 생활용품 잡화 담배 등 기타 소계 음료 등 가공 즉석 (신선일부) 소계 ‘21. 6월 △3.5 △6.0 3.4 2.6 10.0 4.8 9.1 6.0 7월 △9.0 △10.9 1.4 0.2 16.2 0.1 13.3 7.0 8월 △6.1 △9.4 2.1 1 9.1 △0.6 7.4 4.5 9월 11.5 △6.1 6 6.1 14.1 △0.3 11.5 9 10월 11.4 10.6 4.5 5.2 14.9 0.1 12.3 9 11월 7.9 9.7 5.9 6.1 8.8 △0.1 7.2 6.7 12월 21.6 11.0 8.9 9.9 8.8 4.5 8.1 8.9 ‘22. 1월 13.7 8.3 6.4 7.0 12.4 4.8 11.2 9.3 2월 4.8 3.8 9.2 8.7 7.1 1.9 6.3 7.4 3월 7.3 5.1 14.5 13.7 10.6 4.5 9.5 11.5 4월 11.1 3.1 8.9 8.9 13.6 8.2 12.7 10.9 5월 10.7 △1.3 10.6 10.2 14.8 12.2 14.3 12.5 6월 19.9 11.6 7.0 8.1 10.0 4.7 9.1 8.6 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3.9 2.9 5.2 4.1 3.4 0.5 2.8 2.9 2.4 5.1 7.2 7.1 8.2 6.8 9.5 10.6 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비 식품품목 식품 합계 생활용품 잡화 담배 등 기타 소계 음료 등 가공 즉석 (신선일부) 소계 ‘22. 2월 3.4 1.3 42.4 47.1 44.8 8.1 52.9 100.0 ‘22. 3월 3.3 1.2 44.2 48.7 42.9 8.4 51.3 100.0 ‘22. 4월 3.4 1.1 41.3 45.8 45.4 8.8 54.2 100.0 ‘22. 5월 3.6 1.2 40.5 45.3 45.9 8.9 54.7 100.0 ‘22. 6월 3.9 1.2 40.1 45.2 45.8 9.0 54.8 100.0 ㅇ 구매건수 및 구매단가 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 0.1 △1.6 △2.9 2.8 0.3 0.7 7.2 6.6 △0.1 2.5 7.2 12.6 5.5 구매단가 5.9 8.8 7.6 6.1 8.6 6 1.5 2.5 7.5 8.8 3.4 △0.1 3.0 * ‘22.6월 1인당 구매단가 : 6,645원 (전년동월 6,451원) ㅇ 점포당 매출액 증감률 추이 및 점포수 현황 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 점포증가율 6.2 6.3 6.4 6.3 6.2 5.7 5.8 5.9 5.9 6.3 6.5 6.9 7.2 점포당매출액 △0.2 0.7 △1.8 2.5 2.6 0.9 2.9 3.2 1.5 4.9 4.1 5.2 1.3 * ‘22.6월 점포당 매출액 : 5,279.2만원 (전년동월 5,209.9만원) / ’22.6월 점포 수 : 44,180개 □ 준대규모점포(SSM) ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비식품 식품품목 합계 일상용품 생활잡화 소계 농수축산 신선·조리 식품 가공식품 소계 ‘21. 6월 △11.7 △7.6 △9.9 △1.3 △4.4 0.5 △1.5 △2.4 7월 △12.9 △2.9 △8.6 2.5 7.5 3.9 4.2 2.8 8월 △18.9 △5.7 △13.2 △4.4 △7.2 △2.3 △4.4 △5.3 9월 △14.9 △8.1 △11.9 △16.7 △17.3 △15.6 △16.6 △16.1 10월 △12 △0.2 △6.8 0.8 △3 △1.5 △1 △1.6 11월 △13.9 △5.7 △10.2 △6.3 △5.5 △5.7 △5.9 △6.3 12월 △13.9 △3.5 △9.1 △14.3 △11.6 △10.6 △12.5 △12.2 ‘22. 1월 0.3 4.7 2.1 △4.0 △4.2 5.2 △1.5 △1.2 2월 △10.2 △3.0 △7.2 △16.2 △2.0 △2.3 △8.5 △8.4 3월 △4.4 1.3 △2.0 2.3 4.6 11.1 5.3 4.6 4월 △3.3 △3.8 △3.5 △4.5 △1.9 3.4 △1.6 △1.8 5월 △5.1 △1.7 △3.7 △5.6 △2.7 1.7 △2.8 △2.8 6월 △6.9 △4.3 △5.8 △5.1 △2.0 3.6 △1.8 △2.2 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 0.3 △2.0 △3.6 △1.5 2.1△10.0 1.6 △6.1 △4.8△13.9 △5.6 △7.4 △7.0 △9.1 △1.5 △2.3 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비식품 식품품목 합계 일상용품 생활잡화 소계 농수축산 신선·조리 식품 가공식품 소계 ‘22. 2월 5.2 4.1 9.3 37.9 25.2 27.7 90.7 100.0 ‘22. 3월 4.9 3.7 8.6 40.5 24.8 26.1 91.4 100.0 ‘22. 4월 5.1 3.8 8.9 40.0 24.9 26.3 91.1 100.0 ‘22. 5월 5.3 4.1 9.4 39.1 25.1 26.4 90.6 100.0 ‘22. 6월 5.5 4.1 9.5 38.0 25.8 26.6 90.5 100.0 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 △5.6 △3.3 △8.1 △14 △6.3 △9 △10.5 △4.8 △7.0 1.0 △2.1 △2.0 △4.4 구매단가 3.4 6.4 3 △2.5 5 2.9 △1.9 3.8 △1.5 3.6 0.3 △0.8 2.3 점포당 매출 4.0 8.1 △1.1 △12.8 1.8 △3.8 △9.5 0.2 △7.7 5.5 △1.0 △2.1 △1.1 * '22.6월 1인당 구매단가 : 16,610원 (전년동월 16,232원) ** '22.6월 점포당 매출액 : 3.50억원 (전년동월 3.54억원) / ‘22.6월 점포 수 : 1,095개 □ 온라인 유통 ㅇ 전년동월 대비 매출증감률 추이 (단위 : %) 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 19.6 20.2 11.1 14.5 19.7 14.8 12.8 9.1 14.2 7.9 11.0 11.0 9.1 ㅇ 전년동월 대비 매출증감률 추이 (단위 : %) 구분 가전/ 전자 도서/ 문구 패션/ 의류 스포츠 화장품 아동/ 유아 식품 생활/ 가구 서비스/ 기타 합계 ‘21. 6월 3.8 17.7 1.3 △0.9 19.0 △2.7 40.0 6.5 85.7 19.6 7월 30.6 2.3 2.0 △4.8 14.9 △0.6 30.7 4.4 44.9 20.2 8월 4.6 3.2 △1.4 5.1 20.3 △4.6 28.2 4.5 17 11.1 9월 9.6 2.0 4.9 8.4 19.9 △0.6 17.1 9.7 44.9 14.5 10월 22.7 12.5 4.9 5.6 16.2 0.2 25.3 13.4 46.1 19.7 11월 14.6 △1.2 6.3 1.4 19 2.7 19.9 7.3 36.4 14.8 12월 3.9 △4.5 14.3 2.1 17.4 1.5 8.0 26.9 30.3 12.8 ‘22. 1월 △4.2 △9.1 14.6 0.9 24.2 △1.8 18.0 4.3 23.3 9.1 2월 17.0 2.5 7.4 5.0 23.7 4.7 9.8 12.1 26.8 14.2 3월 1.4 0.4 △2.7 △1.4 15.9 5.0 24.6 8.4 1.9 7.9 4월 △0.5 3.9 14.9 △0.6 18.6 5.4 18.1 6.6 24.0 11.0 5월 3.8 2.3 11.9 10.7 26.7 4.5 17.7 3.7 17.6 11.0 6월 1.0 △2.3 6.0 △0.5 18.1 2.1 17.9 8.0 13.6 9.1 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 14.6 13.8 12.6 14.2 19.8 15.4 17.8 20.4 18.4 14.3 17.9 15.2 15.6 15.7 10.2 10.4 ㅇ 상품군별 매출 비중 (단위 : %) 구분 가전/ 전자 도서/ 문구 패션/ 의류 스포츠 화장품 아동/ 유아 식품 생활/ 가구 서비스/ 기타 합계 ‘21. 6월 22.1 1.9 10.2 4.0 4.3 3.6 22.4 15.7 15.8 100.0 7월 24.2 1.9 9.0 4.0 4.3 3.7 22.6 15.4 14.8 100.0 8월 23.3 2 7.5 3.6 4.5 3.7 24.8 15.7 14.9 100.0 9월 22.3 2 8.8 3.9 4.6 3.6 25.6 15.9 13.4 100.0 10월 24.1 1.9 11 4.3 4.4 3.6 21.7 15.6 13.4 100.0 11월 25.1 1.9 11.2 3.9 4.4 3.5 21.1 15.1 13.9 100.0 12월 21.5 2.4 10.3 3.3 4.3 4.6 22.0 18.5 13.0 100.0 ‘22. 1월 21.5 2.1 8.5 2.8 5.0 3.4 27.6 15.0 13.9 100.0 2월 25.3 2.1 7.8 2.7 4.7 3.5 23.1 15.5 15.3 100.0 3월 20.6 2.4 9.3 3.1 4.5 3.6 25.6 15.7 15.1 100.0 4월 19.9 2.1 10.5 3.8 4.8 3.9 24.3 15.2 15.4 100.0 5월 21.7 1.7 10.1 4.0 5.0 3.7 23.5 14.8 15.5 100.0 6월 20.5 1.7 9.9 3.7 4.7 3.4 24.2 15.5 16.4 100.0 ※ 상기 [조사대상 유통업체별 매출 추이]는 동 조사에 협조하는 주요 유통업체별 회계ㆍ정산 과정에서 수정이 있을 시 차기 보도자료에 반영함에 따라, 일부 차이가 발생할 수 있음

닫기 -

0728(29조간)유통물류과, '22년 상반기 및 6월 주요유통업체 매출동향.hwp

미리보기

미리보기

문화체육관광부 보 도 자 료 보도 일시 2022. 7. 28.(목) 11:00 < 7.29.(금) 조간 > 배포 일시 2022. 7. 28.(목) 담당 부서 중견기업정책관 책임자 과 장 정상용 (044-203-4380) 유통물류과 담당자 사무관 박진현 (044-203-4385) ‘22년 상반기 및 6월 주요유통업체 매출동향 - ’22. 7. 28.(목) 배포 - < 일 러 두 기 > 1. 본 동향은 소비동향 파악을 목적으로 주요 온ㆍ오프라인 유통업체의 월간 매출액을 조사‧분석한 자료임 2. 오프라인 유통업체 매출동향은 전체 유통업체가 아닌 주요 오프라인 유통업체 13개사의 월간 매출액을 조사‧분석한 결과임 3. 온라인 유통업체 매출동향은 온라인 유통업체 12개사의 월간 거래액을 조사‧분석한 결과로, 통계청의 승인을 받지 않은 자료임 4. 본 동향은 통계청의 「서비스업동향조사」‧「온라인쇼핑동향조사」와는 모집단, 작성항목 등이 달라 자료간 증감크기나 방향이 상이할 수 있음 ‘22년 상반기 주요 유통업체 매출, 전년 대비 9.3% 증가 - 오프라인 유통업체 8.4% 증가, 온라인 유통업체 10.3% 증가 - ‘22년 6월 주요 유통업체 매출, 전년동월 대비 9.2% 증가 - 오프라인 유통업체 9.3% 증가, 온라인 유통업체 9.1% 증가 - Ⅰ 2022년 상반기 매출동향 [반기] <’18~‘22년 상반기 전년 대비 매출 증감률(%) 추이> <‘21년 및 ’22년 상반기 업태별 매출 구성비(%)> ‘21년 상반기 업태별 매출구성비 ‘22년 상반기 업태별 매출구성비 1. 전체 매출 동향 □ (전체 매출) '22년 상반기 주요 유통업체 매출은 오프라인(8.4%) 부문과 온라인(10.3%) 부문이 모두 성장세를 유지하며, 전년 대비 9.3% 증가 ㅇ (오프라인, 8.4%) 지난해 코로나19 영향에 대한 기저효과와 거리두기 완화에 따라 백화점(18.4%)을 중심으로 매출이 증가 ㅇ (온라인, 10.3%) 온라인을 통한 화장품구매, 장보기 등 온라인ㆍ비대면 소비 문화의 확산이 이어져 매출이 두 자릿수 성장 <‘21년 상반기 vs. ’22년 상반기 매출 비중 및 매출 증감률> 구분 ‘21년 상반기 ‘22년 상반기 매출 비중 매출 증감률 매출 비중 매출 증감률 대형마트 16.3% 0.3% 14.6% △1.5% 백 화 점 16.6% 26.2% 18.0% 18.4% 편 의 점 15.8% 6.2% 15.9% 10.1% S S M 3.2% △10.0% 2.9% △1.9% 오프라인 합계 51.9% 8.6% 51.4% 8.4% 온라인 합계 48.1% 16.1% 48.6% 10.3% 전체 100.0% 12.1% 100.0% 9.3% □ (상품군별 매출비중) 해외여행에 대한 제약이 지속되면서 유명브랜드(0.8%p)의 매출비중이 증가하고, 온라인을 통한 음식배달ㆍe-쿠폰 사용 등이 늘어 서비스/기타(0.6%p) 상품군의 비중도 증가 ㅇ 지난해 코로나19의 영향으로 매출이 늘었던 가전/문화(△0.9%p), 생활/가정(△0.5%p) 등 다른 상품군의 비중은 감소 <’21년 vs. ‘22년 상반기 상품군별 매출구성비(%)> 2. 유통업체별 매출 동향 오프라인 유통업체 □ 지난해 코로나19 영향에 대한 기저효과와 거리두기 완화로 백화점(18.4%) 매출이 큰 폭으로 성장하고 편의점(10.1%)의 매출도 늘어, 대형마트(△1.5%)ㆍSSM(△1.9%)의 매출 감소에도 전체 오프라인 매출은 8.4% 증가 ㅇ (대형마트) 가정/생활(△3.7%), 가전/문화(△3.6%) 등 매출 감소로 카페 및 푸드코트 등 기타(3.7%), 의류(0.6%)의 매출 회복이 있었으나, 전체 매출(△1.5%) 소폭 감소 ㅇ (백화점) 유명브랜드(26.9%), 아동/스포츠(26.3%), 여성의류(정장 17.1%, 캐주얼16.1%), 남성의류(19.8%) 등 전 상품군의 매출이 호조세를 이어가 전체 매출(18.4%) 크게 증가 ㅇ (편의점) 근거리ㆍ소량구매 선호에 따라 가공‧즉석 등 식품군(10.6%)의 매출이 늘고 생활용품(11.5%)의 매출도 증가해 전체 매출(10.1%) 증가 ㅇ (준대규모점포(SSM)) 온라인으로 구매채널이 이동한 일상용품(△4.9%)‧생활잡화(△1.1%) 등 비식품군(△3.3%)과 식품군(△1.7%) 매출이 모두 감소하여 전체 매출(△1.9%) 감소 <’22년 상반기 오프라인 업태별 전년 대비 매출 증감률 (단위: %)> 구분 전체 대형마트 백화점 편의점 SSM 매출 증감률 8.4 △1.5 18.4 10.1 △1.9 온라인 유통업체 □ 온라인을 통한 장보기 등의 보편화로 식품(17.8%) 분야 매출이 증가하며 전체 온라인 매출 10.3% 증가 ㅇ 야외활동 재개에 따른 화장품(21.2%), 음식배달ㆍ공연티켓 등의 서비스/기타(17.0%) 매출이 가파르게 성장 Ⅰ 2022년 6월 매출동향 [월간] <‘22년 6월 기준 전년동월 대비 매출 증감률(%)> 온‧오프라인 매출 증감률 오프라인 업태별 매출 증감률 1. 전체 매출 동향 □ (전체 매출) 오프라인 부문(9.3%)과 온라인 부문(9.1%)이 고른 성장세를 보이며, 전체 매출은 전년동월 대비 9.2% 상승 ㅇ (오프라인) 거리두기 완화 등 야외활동 증가와 보복소비 영향으로 아동/스포츠(24.1%)를 비롯, 모든 품목에서 매출 상승 ㅇ (온라인) 실외활동과 모임 증가로 화장품・식품 등 온라인 구매와 서비스(공연·레저 상품 예약) 수요가 지속되며 전 품목에서 매출 상승 * 오프라인/온라인 매출규모(조원) : (‘22.4월) 7.01 / 6.59 ⇒ (‘22.5월) 7.48 / 6.97 ⇒ (’22.6월) 7.08 / 6.50 <주요 유통업체의 전년동월 대비 월별 매출 증감률 (단위 : %)> 구분 ‘21년 ‘22년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 전체 11.4 13.1 6.4 8.2 14.4 9.6 11.6 13.9 4.7 7.1 10.6 10.1 9.2 오프라인 4.8 7.0 2.5 3.3 10 4.6 10.3 18.4 △3.8 6.3 10.2 9.3 9.3 온라인 19.6 20.2 11.1 14.5 19.7 14.8 12.8 9.1 14.2 7.9 11.0 11.0 9.1 □ (상품군별 매출) 해외유명브랜드(19.6%), 패션/잡화(11.7%), 서비스/기타(10.8%), 아동/스포츠(9.2%) 등 전체 상품군 매출 상승 ㅇ (오프라인) 아동/스포츠(24.1%), 해외유명브랜드(19.6%)와 패션/잡화(13.9%) 분야가 큰 폭으로 상승하면서 전체 상품군에서 매출 상승 ㅇ (온라인) 식품(17.9%), 서비스/기타(13.6%), 패션/잡화(9.6%) 등 판매호조세가 이어지면서 전체 상품군에서 매출 상승 <’22년 6월 전년동월 대비 상품군별 매출 증감률 (단위 : %)> 구분 전체 가전/ 문화 패션/ 잡화 아동/ 스포츠 식품 생활/ 가정 서비스/ 기타 해외유명 브랜드 전체 (비중,%) 9.2 (100) 0.8 (12.1) 11.7 (13.7) 9.2 (5.8) 9.5 (34.5) 7.7 (12.6) 10.8 (15.2) 19.6 (6.1) 오프라인 9.3 1.0 13.9 24.1 5.6 7.3 8.0 19.6 온라인 9.1 0.8 9.6 0.7 17.9 8.0 13.6 - □ (구매건수ㆍ구매단가) 백화점·편의점 방문객 증가, 대형마트·SSM 방문객 감소 추세가 지속(`22.4월~6월), 전체 구매건수(4.3%) 증가와 함께 농·축산물 등 물가상승 영향으로 전체 구매단가(4.7%)도 증가 <’22년 6월 오프라인 부문 구매건수ㆍ단가 증감률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 구매건수 4.3 △2.9 9.8 5.5 △4.4 구매단가 4.7 5.3 7.7 3.0 2.3 * 온라인은 구매건수를 집계하지 않고 있어 통계자료에 미포함 □ (업태별 매출 비중) 전년 동월 대비 오프라인·온라인 매출 비중은 유사 ㅇ 오프라인 업태 중 백화점(1.4%p)의 매출 비중은 늘고, 대형마트(△0.9%p)·SSM(△0.3%p)은 감소, 편의점은 변동 없음 <’21년 vs. ’22년 6월 업태별 매출구성비> ’21년 6월 업태별 매출구성비 ’22년 6월 업태별 매출구성비 2. 유통업체별 매출 동향 오프라인 유통업체 □ 대형마트(2.3%)ㆍ백화점(18.2%)ㆍ편의점(8.6%)의 매출은 증가하고, SSM(△2.2%)의 매출은 감소하였으며 전체 매출은 9.3% 증가 ㅇ (대형마트) 거리두기 완화에 따른 야외활동 증가 등으로 의류(5.3%), 잡화(2.3%) 등 전 품목에서 소폭 성장하면서 전체 매출은 2.3% 증가 ㅇ (백화점) 방문객수 증가(구매건수 9.8%) 추세가 지속되었고, 전 품목에서 판매호조(아동/스포츠 27.4%, 남성의류 18.7%, 여성정장 17.8% 등)를 보이며 전체 매출은 18.2% 증가 ㅇ (편의점) 정상 등교·근무 등으로 이용객수가 늘며, 생활용품(19.9%), 잡화(11.6%), 가공식품(10.0%) 등 전 품목 판매호조로 전체 매출 8.6% 증가 ㅇ (준대규모점포) 가공식품(3.6%)을 제외한 일상용품(△6.9%), 농·수축산(△5.1%) 등 대부분 품목의 판매 부진으로 전체 매출은 2.2% 감소 <’22년 6월 오프라인 업태별 전년동월 대비 매출 증감률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 매출 증감률 9.3 2.3 18.2 8.6 △2.2 □ (점포당 매출) 점포수는 대형마트·SSM은 감소, 백화점·편의점은 증가하였으며, 점포당 매출은 SSM을 제외한 대부분 업태에서 증가 <’22년 6월 전년동월 대비 점포당 매출 및 점포수 증강률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 점포당 매출 증감률 13.0 4.7 14.2 1.3 △1.1 점포 수 증감률 6.9 △2.3 3.4 7.2 △1.1 온라인 유통업체 □ 온라인 유통업체 매출은 전년동월 대비 9.1% 증가하였으며, 도서/문구(△2.3%), 스포츠(△0.5%) 품목을 제외한 대부분 품목에서 매출이 상승 ㅇ 모임·실외활동 증가에 따른 화장품(18.1%) 및 가공식품·식음료 등 식품(17.9%) 수요증가, 여행·공연 예약상품 등 서비스/기타(13.6%) 품목의 판매호조 지속 <‘22년 6월 상품군별 전년동월 대비 매출증감률‧매출비중 (단위 : %)> 구분 전체 가전 전자 도서 문구 패션 의류 스포츠 화장품 아동 유아 식품 생활 가구 서비스기타 매출증감률 9.1 1.0 △2.3 6.0 △0.5 18.1 2.1 17.9 8.0 13.6 매출비중 100.0 20.5 1.7 9.9 3.7 4.7 3.4 24.2 15.5 16.4 참고 조사대상 및 유사통계 간 비교 【 (참고1) 매출동향 조사대상 】 □ 오프라인 유통업체(13개사) ∙ 백화점(3) : 롯데백화점, 현대백화점, 신세계백화점 ∙ 대형마트(3) : 이마트, 홈플러스, 롯데마트 ∙ 편의점(3) : 지에스25, 씨유, 세븐일레븐(바이더웨이 포함) ∙ 준대규모점포(SSM)(4) : 이마트에브리데이, 롯데슈퍼, 지에스더후레쉬, 홈플러스익스프레스 □ 온라인 유통업체(12개사) ∙ G마켓글로벌(G마켓‧옥션), 11번가, 인터파크, 쿠팡, SSG(이마트‧신세계), 에이케이몰, 홈플러스, 갤러리아몰, 롯데마트, 롯데온, 위메프, 티몬 ※ 유통업체별 협회(백화점·체인스토어·온라인쇼핑협회) 및 개별 유통업체(편의점)를 통해 조사 【 (참고2) 유사통계 간 비교 】 통계 명 주요 유통업체 (오프라인) 매출동향조사 서비스업동향조사 온라인쇼핑동향조사 작성기관 산업통상자원부 통계청 작성목적 소비동향 파악 서비스업‧도소매업 사업체의 경영실태 파악 온라인쇼핑동향 분석 모집단 주요 오프라인 유통업체 (13개사) 국내에서 서비스업을 운영하는 사업체 전체 연간거래액이 24백만원 이상인 온라인쇼핑 운영업체 (13,000여개) 표본추출틀 주요 오프라인 유통업체 (13개사) 2015 경제총조사 결과, 한국표준산업분류 대분류 13개 업종 공정위 PG사, 새올 행정시스템, 경총자료 조사대상 주요 오프라인 유통업체 13개사 (유의표본) 표본 17,300개 사업체 표본 1,100개 사업체 포괄범위 상품 및 서비스 거래금액 판매액(상품) 23개 상품군별 상품 및 서비스 거래금액 붙임 조사대상 유통업체별 매출 추이 □ 대형마트 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비 식품 식품 합계 가전/문화 의류 가정/생활 스포츠 잡화 기타 소계 ‘21. 6월 △15.2 △10.4 △15.3 △8.4 △29.4 0.0 △14.6 6.0 △2.4 7월 15.0 △3.5 △7.4 11.8 △4.1 △1.5 1.3 10.9 7.3 8월 △14.9 △19.1 △16.1 △13.6 △33.2 △10.8 △16.5 0.4 △5.5 9월 △5.5 △1.1 △14 5.1 △14.4 8.1 △8.6 △15.3 △13.3 10월 9.6 △1.5 △6.8 △10.4 △21.2 △5.4 △1.8 3.5 1.4 11월 △17.8 △1.8 △14.8 △13.7 △17.2 0.1 △13.6 △8.3 △10.3 12월 △6.1 7.9 △7.7 5.2 6.3 30.1 △2.3 △7.9 △6.1 ‘22. 1월 △2.7 13.1 13.5 6.4 10.6 16.9 6.8 16.9 13.8 2월 0.5 △20.5 △24.1 △13.3 △20.5 △7.1 △14.6 △28.7 △24.0 3월 △8.0 △17.8 △5.3 △13.9 △16.1 △4.4 △9.0 4.8 0.0 4월 △0.6 13.2 △2.7 1.8 10.8 5.3 1.3 2.3 2.0 5월 △9.7 9.0 △3.9 5.3 6.0 3.0 △3.1 △3.2 △3.0 6월 1.0 5.3 1.1 1.4 2.3 8.2 1.8 2.3 2.3 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 △8.1 △4.0 △5.1 △5.8 △5.5 △0.7 0.1 △3.0 0.4 0.2 △4.7 △5 △2.3 △3.2 0.3 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비 식품 식품 합계 가전/문화 의류 가정/생활 스포츠 잡화 기타 소계 ‘22. 2월 14.0 3.4 14.0 1.3 1.6 2.0 36.4 63.6 100 ‘22. 3월 11.0 3.5 12.7 1.3 1.8 2.1 32.4 67.6 100 ‘22. 4월 10.7 4.9 12.4 1.7 2.3 2.2 34.2 65.8 100 ‘22. 5월 11.7 5.3 13.0 2.0 2.5 2.4 36.9 63.1 100 ‘22. 6월 10.8 4.8 14.1 1.8 2.3 2.4 36.2 63.8 100 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 △1.8 △1.3 △11.5 △16.1 △9.7 △11.5 △7.3 2.9 △13.1 △2.8 △4.1 △5.0 △2.9 구매단가 △0.6 8.7 6.8 3.4 12.4 1.3 1.3 10.6 △12.5 2.9 6.4 2.1 5.3 점포당 매출 0.9 11.2 △5.5 △10.8 4.1 △7.5 △3.2 17.4 △22.2 5.5 3.9 △1.5 4.7 * '22.6월 1인당 구매단가 : 52,041원 (전년동월 49,406원) ** '22.6월 점포당 매출액 : 49.6억원 (전년동월 47.4억원) / ‘22.6월 점포 수 : 381개 □ 백화점 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비식품품목 식품 합계 잡 화 여성 정장 여성 캐주얼 남성 의류 아동 스포츠 가정 용품 해외유명 브랜드 소계 ‘21. 6월 △5.4 4.1 4.1 4.9 17.0 △0.5 31.5 12.9 10.8 12.8 7월 △9.2 △9.5 0.9 △0.6 16.5 16.5 18.8 9.5 △2.6 7.8 8월 △2.6 1.5 △6.8 4.5 24.8 25.6 18.6 14.3 4.5 13 9월 12.5 19.3 23.6 27 36.9 17.4 38.1 27.3 11.8 24.3 10월 5.0 7.7 5.4 12.8 19.6 22.2 39.4 21.5 16.9 21 11월 7.3 15 13.3 14.9 25.7 3 32.9 18.9 13.1 18.3 12월 30.6 36.1 48.6 40.5 55.3 14.6 42.8 37.7 28.3 36.5 ‘22. 1월 31.0 23.7 35.5 38.7 46.3 6.9 46.5 32.7 60.0 37.2 2월 3.2 13.8 1.9 10.8 11.9 9.3 32.5 17.4 △30.3 9.3 3월 △2.4 6.9 △2.7 3.8 12.6 △5.4 21.1 8.7 0.2 7.8 4월 14.7 19.2 22.2 21.2 33.4 6.8 22.5 20.0 10.4 19.1 5월 21.9 22.7 25.3 24.5 30.0 3.1 23.6 20.8 12.4 19.9 6월 14.4 17.8 17.3 18.7 27.4 10.6 19.6 18.1 16.2 18.2 * 자료 : 해외유명브랜드는 각사 분류 기준 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 1.0 △1.7 △0.2 △0.1 △19.9 △8.4 △5.0 △6.0 △9.8 31.2 21.5 14.6 24.8 24.1 17.6 19.1 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비식품품목 식품 합계 잡 화 여성 정장 여성 캐주얼 남성 의류 아동 스포츠 가정 용품 해외유명 브랜드 소계 ’22. 2월 9.7 6.7 5.3 3.4 10.3 16.4 37.3 89.2 10.8 100 ’22. 3월 9.4 8.2 6.2 4.1 11.5 13.4 36.4 89.1 10.9 100 ‘22. 4월 10.3 7.0 6.7 4.6 12.8 13.1 34.9 89.4 10.6 100 ‘22. 5월 12.0 6.8 6.8 4.5 12.4 13.2 33.4 89.0 11.0 100 ‘22. 6월 11.7 6.5 7.4 4.2 11.8 13.5 33.5 88.6 11.4 100 * 자료 : 해외유명브랜드는 각사 분류 기준 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 1.4 △8.1 △6.8 13 7.1 7.5 29.6 21.2 △1.5 △7.2 7.8 11.4 9.8 구매단가 11.2 17.3 21.2 10 13 10.1 5.3 13.3 10.9 16.1 10.4 7.6 7.7 점포당 매출 10.8 5.9 9.2 18.1 15 12.4 29.7 30.4 5.6 4.2 15.1 15.9 14.2 * '22.6월 1인당 구매단가 : 114,201원 (전년동월 106,057원) ** '22.6월 점포당 매출액 : 413.3억원 (전년동월 361.8억원) / ‘22.6월 점포 수 : 60개 □ 편의점 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비 식품품목 식품 합계 생활용품 잡화 담배 등 기타 소계 음료 등 가공 즉석 (신선일부) 소계 ‘21. 6월 △3.5 △6.0 3.4 2.6 10.0 4.8 9.1 6.0 7월 △9.0 △10.9 1.4 0.2 16.2 0.1 13.3 7.0 8월 △6.1 △9.4 2.1 1 9.1 △0.6 7.4 4.5 9월 11.5 △6.1 6 6.1 14.1 △0.3 11.5 9 10월 11.4 10.6 4.5 5.2 14.9 0.1 12.3 9 11월 7.9 9.7 5.9 6.1 8.8 △0.1 7.2 6.7 12월 21.6 11.0 8.9 9.9 8.8 4.5 8.1 8.9 ‘22. 1월 13.7 8.3 6.4 7.0 12.4 4.8 11.2 9.3 2월 4.8 3.8 9.2 8.7 7.1 1.9 6.3 7.4 3월 7.3 5.1 14.5 13.7 10.6 4.5 9.5 11.5 4월 11.1 3.1 8.9 8.9 13.6 8.2 12.7 10.9 5월 10.7 △1.3 10.6 10.2 14.8 12.2 14.3 12.5 6월 19.9 11.6 7.0 8.1 10.0 4.7 9.1 8.6 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3.9 2.9 5.2 4.1 3.4 0.5 2.8 2.9 2.4 5.1 7.2 7.1 8.2 6.8 9.5 10.6 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비 식품품목 식품 합계 생활용품 잡화 담배 등 기타 소계 음료 등 가공 즉석 (신선일부) 소계 ‘22. 2월 3.4 1.3 42.4 47.1 44.8 8.1 52.9 100.0 ‘22. 3월 3.3 1.2 44.2 48.7 42.9 8.4 51.3 100.0 ‘22. 4월 3.4 1.1 41.3 45.8 45.4 8.8 54.2 100.0 ‘22. 5월 3.6 1.2 40.5 45.3 45.9 8.9 54.7 100.0 ‘22. 6월 3.9 1.2 40.1 45.2 45.8 9.0 54.8 100.0 ㅇ 구매건수 및 구매단가 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 0.1 △1.6 △2.9 2.8 0.3 0.7 7.2 6.6 △0.1 2.5 7.2 12.6 5.5 구매단가 5.9 8.8 7.6 6.1 8.6 6 1.5 2.5 7.5 8.8 3.4 △0.1 3.0 * ‘22.6월 1인당 구매단가 : 6,645원 (전년동월 6,451원) ㅇ 점포당 매출액 증감률 추이 및 점포수 현황 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 점포증가율 6.2 6.3 6.4 6.3 6.2 5.7 5.8 5.9 5.9 6.3 6.5 6.9 7.2 점포당매출액 △0.2 0.7 △1.8 2.5 2.6 0.9 2.9 3.2 1.5 4.9 4.1 5.2 1.3 * ‘22.6월 점포당 매출액 : 5,279.2만원 (전년동월 5,209.9만원) / ’22.6월 점포 수 : 44,180개 □ 준대규모점포(SSM) ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비식품 식품품목 합계 일상용품 생활잡화 소계 농수축산 신선·조리식품 가공식품 소계 ‘21. 6월 △11.7 △7.6 △9.9 △1.3 △4.4 0.5 △1.5 △2.4 7월 △12.9 △2.9 △8.6 2.5 7.5 3.9 4.2 2.8 8월 △18.9 △5.7 △13.2 △4.4 △7.2 △2.3 △4.4 △5.3 9월 △14.9 △8.1 △11.9 △16.7 △17.3 △15.6 △16.6 △16.1 10월 △12 △0.2 △6.8 0.8 △3 △1.5 △1 △1.6 11월 △13.9 △5.7 △10.2 △6.3 △5.5 △5.7 △5.9 △6.3 12월 △13.9 △3.5 △9.1 △14.3 △11.6 △10.6 △12.5 △12.2 ‘22. 1월 0.3 4.7 2.1 △4.0 △4.2 5.2 △1.5 △1.2 2월 △10.2 △3.0 △7.2 △16.2 △2.0 △2.3 △8.5 △8.4 3월 △4.4 1.3 △2.0 2.3 4.6 11.1 5.3 4.6 4월 △3.3 △3.8 △3.5 △4.5 △1.9 3.4 △1.6 △1.8 5월 △5.1 △1.7 △3.7 △5.6 △2.7 1.7 △2.8 △2.8 6월 △6.9 △4.3 △5.8 △5.1 △2.0 3.6 △1.8 △2.2 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 0.3 △2.0 △3.6 △1.5 2.1 △10.0 1.6 △6.1 △4.8 △13.9 △5.6 △7.4 △7.0 △9.1 △1.5 △2.3 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비식품 식품품목 합계 일상용품 생활잡화 소계 농수축산 신선·조리식품 가공식품 소계 ‘22. 2월 5.2 4.1 9.3 37.9 25.2 27.7 90.7 100.0 ‘22. 3월 4.9 3.7 8.6 40.5 24.8 26.1 91.4 100.0 ‘22. 4월 5.1 3.8 8.9 40.0 24.9 26.3 91.1 100.0 ‘22. 5월 5.3 4.1 9.4 39.1 25.1 26.4 90.6 100.0 ‘22. 6월 5.5 4.1 9.5 38.0 25.8 26.6 90.5 100.0 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 △5.6 △3.3 △8.1 △14 △6.3 △9 △10.5 △4.8 △7.0 1.0 △2.1 △2.0 △4.4 구매단가 3.4 6.4 3 △2.5 5 2.9 △1.9 3.8 △1.5 3.6 0.3 △0.8 2.3 점포당 매출 4.0 8.1 △1.1 △12.8 1.8 △3.8 △9.5 0.2 △7.7 5.5 △1.0 △2.1 △1.1 * '22.6월 1인당 구매단가 : 16,610원 (전년동월 16,232원) ** '22.6월 점포당 매출액 : 3.50억원 (전년동월 3.54억원) / ‘22.6월 점포 수 : 1,095개 □ 온라인 유통 ㅇ 전년동월 대비 매출증감률 추이 (단위 : %) 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 19.6 20.2 11.1 14.5 19.7 14.8 12.8 9.1 14.2 7.9 11.0 11.0 9.1 ㅇ 전년동월 대비 매출증감률 추이 (단위 : %) 구분 가전/ 전자 도서/ 문구 패션/ 의류 스포츠 화장품 아동/ 유아 식품 생활/ 가구 서비스/ 기타 합계 ‘21. 6월 3.8 17.7 1.3 △0.9 19.0 △2.7 40.0 6.5 85.7 19.6 7월 30.6 2.3 2.0 △4.8 14.9 △0.6 30.7 4.4 44.9 20.2 8월 4.6 3.2 △1.4 5.1 20.3 △4.6 28.2 4.5 17 11.1 9월 9.6 2.0 4.9 8.4 19.9 △0.6 17.1 9.7 44.9 14.5 10월 22.7 12.5 4.9 5.6 16.2 0.2 25.3 13.4 46.1 19.7 11월 14.6 △1.2 6.3 1.4 19 2.7 19.9 7.3 36.4 14.8 12월 3.9 △4.5 14.3 2.1 17.4 1.5 8.0 26.9 30.3 12.8 ‘22. 1월 △4.2 △9.1 14.6 0.9 24.2 △1.8 18.0 4.3 23.3 9.1 2월 17.0 2.5 7.4 5.0 23.7 4.7 9.8 12.1 26.8 14.2 3월 1.4 0.4 △2.7 △1.4 15.9 5.0 24.6 8.4 1.9 7.9 4월 △0.5 3.9 14.9 △0.6 18.6 5.4 18.1 6.6 24.0 11.0 5월 3.8 2.3 11.9 10.7 26.7 4.5 17.7 3.7 17.6 11.0 6월 1.0 △2.3 6.0 △0.5 18.1 2.1 17.9 8.0 13.6 9.1 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 14.6 13.8 12.6 14.2 19.8 15.4 17.8 20.4 18.4 14.3 17.9 15.2 15.6 15.7 10.2 10.4 ㅇ 상품군별 매출 비중 (단위 : %) 구분 가전/ 전자 도서/ 문구 패션/ 의류 스포츠 화장품 아동/ 유아 식품 생활/ 가구 서비스/ 기타 합계 ‘21. 6월 22.1 1.9 10.2 4.0 4.3 3.6 22.4 15.7 15.8 100.0 7월 24.2 1.9 9.0 4.0 4.3 3.7 22.6 15.4 14.8 100.0 8월 23.3 2 7.5 3.6 4.5 3.7 24.8 15.7 14.9 100.0 9월 22.3 2 8.8 3.9 4.6 3.6 25.6 15.9 13.4 100.0 10월 24.1 1.9 11 4.3 4.4 3.6 21.7 15.6 13.4 100.0 11월 25.1 1.9 11.2 3.9 4.4 3.5 21.1 15.1 13.9 100.0 12월 21.5 2.4 10.3 3.3 4.3 4.6 22.0 18.5 13.0 100.0 ‘22. 1월 21.5 2.1 8.5 2.8 5.0 3.4 27.6 15.0 13.9 100.0 2월 25.3 2.1 7.8 2.7 4.7 3.5 23.1 15.5 15.3 100.0 3월 20.6 2.4 9.3 3.1 4.5 3.6 25.6 15.7 15.1 100.0 4월 19.9 2.1 10.5 3.8 4.8 3.9 24.3 15.2 15.4 100.0 5월 21.7 1.7 10.1 4.0 5.0 3.7 23.5 14.8 15.5 100.0 6월 20.5 1.7 9.9 3.7 4.7 3.4 24.2 15.5 16.4 100.0 ※ 상기 [조사대상 유통업체별 매출 추이]는 동 조사에 협조하는 주요 유통업체별 회계ㆍ정산 과정에서 수정이 있을 시 차기 보도자료에 반영함에 따라, 일부 차이가 발생할 수 있음

닫기 -

0728(29조간)유통물류과, '22년 상반기 및 6월 주요유통업체 매출동향.hwpx

미리보기

미리보기

문화체육관광부 보 도 자 료 보도 일시 2022. 7. 28.(목) 11:00 < 7.29.(금) 조간 > 배포 일시 2022. 7. 28.(목) 담당 부서 중견기업정책관 책임자 과 장 정상용 (044-203-4380) 유통물류과 담당자 사무관 박진현 (044-203-4385) ‘22년 상반기 및 6월 주요유통업체 매출동향 - ’22. 7. 28.(목) 배포 - < 일 러 두 기 > 1. 본 동향은 소비동향 파악을 목적으로 주요 온ㆍ오프라인 유통업체의 월간 매출액을 조사‧분석한 자료임 2. 오프라인 유통업체 매출동향은 전체 유통업체가 아닌 주요 오프라인 유통업체 13개사의 월간 매출액을 조사‧분석한 결과임 3. 온라인 유통업체 매출동향은 온라인 유통업체 12개사의 월간 거래액을 조사‧분석한 결과로, 통계청의 승인을 받지 않은 자료임 4. 본 동향은 통계청의 「서비스업동향조사」‧「온라인쇼핑동향조사」와는 모집단, 작성항목 등이 달라 자료간 증감크기나 방향이 상이할 수 있음 ‘22년 상반기 주요 유통업체 매출, 전년 대비 9.3% 증가 - 오프라인 유통업체 8.4% 증가, 온라인 유통업체 10.3% 증가 - ‘22년 6월 주요 유통업체 매출, 전년동월 대비 9.2% 증가 - 오프라인 유통업체 9.3% 증가, 온라인 유통업체 9.1% 증가 - Ⅰ 2022년 상반기 매출동향 [반기] <’18~‘22년 상반기 전년 대비 매출 증감률(%) 추이> <‘21년 및 ’22년 상반기 업태별 매출 구성비(%)> ‘21년 상반기 업태별 매출구성비 ‘22년 상반기 업태별 매출구성비 1. 전체 매출 동향 □ (전체 매출) '22년 상반기 주요 유통업체 매출은 오프라인(8.4%) 부문과 온라인(10.3%) 부문이 모두 성장세를 유지하며, 전년 대비 9.3% 증가 ㅇ (오프라인, 8.4%) 지난해 코로나19 영향에 대한 기저효과와 거리두기 완화에 따라 백화점(18.4%)을 중심으로 매출이 증가 ㅇ (온라인, 10.3%) 온라인을 통한 화장품구매, 장보기 등 온라인ㆍ비대면 소비 문화의 확산이 이어져 매출이 두 자릿수 성장 <‘21년 상반기 vs. ’22년 상반기 매출 비중 및 매출 증감률> 구분 ‘21년 상반기 ‘22년 상반기 매출 비중 매출 증감률 매출 비중 매출 증감률 대형마트 16.3% 0.3% 14.6% △1.5% 백 화 점 16.6% 26.2% 18.0% 18.4% 편 의 점 15.8% 6.2% 15.9% 10.1% S S M 3.2% △10.0% 2.9% △1.9% 오프라인 합계 51.9% 8.6% 51.4% 8.4% 온라인 합계 48.1% 16.1% 48.6% 10.3% 전체 100.0% 12.1% 100.0% 9.3% □ (상품군별 매출비중) 해외여행에 대한 제약이 지속되면서 유명브랜드(0.8%p)의 매출비중이 증가하고, 온라인을 통한 음식배달ㆍe-쿠폰 사용 등이 늘어 서비스/기타(0.6%p) 상품군의 비중도 증가 ㅇ 지난해 코로나19의 영향으로 매출이 늘었던 가전/문화(△0.9%p), 생활/가정(△0.5%p) 등 다른 상품군의 비중은 감소 <’21년 vs. ‘22년 상반기 상품군별 매출구성비(%)> 2. 유통업체별 매출 동향 오프라인 유통업체 □ 지난해 코로나19 영향에 대한 기저효과와 거리두기 완화로 백화점(18.4%) 매출이 큰 폭으로 성장하고 편의점(10.1%)의 매출도 늘어, 대형마트(△1.5%)ㆍSSM(△1.9%)의 매출 감소에도 전체 오프라인 매출은 8.4% 증가 ㅇ (대형마트) 가정/생활(△3.7%), 가전/문화(△3.6%) 등 매출 감소로 카페 및 푸드코트 등 기타(3.7%), 의류(0.6%)의 매출 회복이 있었으나, 전체 매출(△1.5%) 소폭 감소 ㅇ (백화점) 유명브랜드(26.9%), 아동/스포츠(26.3%), 여성의류(정장 17.1%, 캐주얼16.1%), 남성의류(19.8%) 등 전 상품군의 매출이 호조세를 이어가 전체 매출(18.4%) 크게 증가 ㅇ (편의점) 근거리ㆍ소량구매 선호에 따라 가공‧즉석 등 식품군(10.6%)의 매출이 늘고 생활용품(11.5%)의 매출도 증가해 전체 매출(10.1%) 증가 ㅇ (준대규모점포(SSM)) 온라인으로 구매채널이 이동한 일상용품(△4.9%)‧생활잡화(△1.1%) 등 비식품군(△3.3%)과 식품군(△1.7%) 매출이 모두 감소하여 전체 매출(△1.9%) 감소 <’22년 상반기 오프라인 업태별 전년 대비 매출 증감률 (단위: %)> 구분 전체 대형마트 백화점 편의점 SSM 매출 증감률 8.4 △1.5 18.4 10.1 △1.9 온라인 유통업체 □ 온라인을 통한 장보기 등의 보편화로 식품(17.8%) 분야 매출이 증가하며 전체 온라인 매출 10.3% 증가 ㅇ 야외활동 재개에 따른 화장품(21.2%), 음식배달ㆍ공연티켓 등의 서비스/기타(17.0%) 매출이 가파르게 성장 Ⅰ 2022년 6월 매출동향 [월간] <‘22년 6월 기준 전년동월 대비 매출 증감률(%)> 온‧오프라인 매출 증감률 오프라인 업태별 매출 증감률 1. 전체 매출 동향 □ (전체 매출) 오프라인 부문(9.3%)과 온라인 부문(9.1%)이 고른 성장세를 보이며, 전체 매출은 전년동월 대비 9.2% 상승 ㅇ (오프라인) 거리두기 완화 등 야외활동 증가와 보복소비 영향으로 아동/스포츠(24.1%)를 비롯, 모든 품목에서 매출 상승 ㅇ (온라인) 실외활동과 모임 증가로 화장품・식품 등 온라인 구매와 서비스(공연·레저 상품 예약) 수요가 지속되며 전 품목에서 매출 상승 * 오프라인/온라인 매출규모(조원) : (‘22.4월) 7.01 / 6.59 ⇒ (‘22.5월) 7.48 / 6.97 ⇒ (’22.6월) 7.08 / 6.50 <주요 유통업체의 전년동월 대비 월별 매출 증감률 (단위 : %)> 구분 ‘21년 ‘22년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 전체 11.4 13.1 6.4 8.2 14.4 9.6 11.6 13.9 4.7 7.1 10.6 10.1 9.2 오프라인 4.8 7.0 2.5 3.3 10 4.6 10.3 18.4 △3.8 6.3 10.2 9.3 9.3 온라인 19.6 20.2 11.1 14.5 19.7 14.8 12.8 9.1 14.2 7.9 11.0 11.0 9.1 □ (상품군별 매출) 해외유명브랜드(19.6%), 패션/잡화(11.7%), 서비스/기타(10.8%), 아동/스포츠(9.2%) 등 전체 상품군 매출 상승 ㅇ (오프라인) 아동/스포츠(24.1%), 해외유명브랜드(19.6%)와 패션/잡화(13.9%) 분야가 큰 폭으로 상승하면서 전체 상품군에서 매출 상승 ㅇ (온라인) 식품(17.9%), 서비스/기타(13.6%), 패션/잡화(9.6%) 등 판매호조세가 이어지면서 전체 상품군에서 매출 상승 <’22년 6월 전년동월 대비 상품군별 매출 증감률 (단위 : %)> 구분 전체 가전/ 문화 패션/ 잡화 아동/ 스포츠 식품 생활/ 가정 서비스/ 기타 해외유명 브랜드 전체 (비중,%) 9.2 (100) 0.8 (12.1) 11.7 (13.7) 9.2 (5.8) 9.5 (34.5) 7.7 (12.6) 10.8 (15.2) 19.6 (6.1) 오프라인 9.3 1.0 13.9 24.1 5.6 7.3 8.0 19.6 온라인 9.1 0.8 9.6 0.7 17.9 8.0 13.6 - □ (구매건수ㆍ구매단가) 백화점·편의점 방문객 증가, 대형마트·SSM 방문객 감소 추세가 지속(`22.4월~6월), 전체 구매건수(4.3%) 증가와 함께 농·축산물 등 물가상승 영향으로 전체 구매단가(4.7%)도 증가 <’22년 6월 오프라인 부문 구매건수ㆍ단가 증감률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 구매건수 4.3 △2.9 9.8 5.5 △4.4 구매단가 4.7 5.3 7.7 3.0 2.3 * 온라인은 구매건수를 집계하지 않고 있어 통계자료에 미포함 □ (업태별 매출 비중) 전년 동월 대비 오프라인·온라인 매출 비중은 유사 ㅇ 오프라인 업태 중 백화점(1.4%p)의 매출 비중은 늘고, 대형마트(△0.9%p)·SSM(△0.3%p)은 감소, 편의점은 변동 없음 <’21년 vs. ’22년 6월 업태별 매출구성비> ’21년 6월 업태별 매출구성비 ’22년 6월 업태별 매출구성비 2. 유통업체별 매출 동향 오프라인 유통업체 □ 대형마트(2.3%)ㆍ백화점(18.2%)ㆍ편의점(8.6%)의 매출은 증가하고, SSM(△2.2%)의 매출은 감소하였으며 전체 매출은 9.3% 증가 ㅇ (대형마트) 거리두기 완화에 따른 야외활동 증가 등으로 의류(5.3%), 잡화(2.3%) 등 전 품목에서 소폭 성장하면서 전체 매출은 2.3% 증가 ㅇ (백화점) 방문객수 증가(구매건수 9.8%) 추세가 지속되었고, 전 품목에서 판매호조(아동/스포츠 27.4%, 남성의류 18.7%, 여성정장 17.8% 등)를 보이며 전체 매출은 18.2% 증가 ㅇ (편의점) 정상 등교·근무 등으로 이용객수가 늘며, 생활용품(19.9%), 잡화(11.6%), 가공식품(10.0%) 등 전 품목 판매호조로 전체 매출 8.6% 증가 ㅇ (준대규모점포) 가공식품(3.6%)을 제외한 일상용품(△6.9%), 농·수축산(△5.1%) 등 대부분 품목의 판매 부진으로 전체 매출은 2.2% 감소 <’22년 6월 오프라인 업태별 전년동월 대비 매출 증감률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 매출 증감률 9.3 2.3 18.2 8.6 △2.2 □ (점포당 매출) 점포수는 대형마트·SSM은 감소, 백화점·편의점은 증가하였으며, 점포당 매출은 SSM을 제외한 대부분 업태에서 증가 <’22년 6월 전년동월 대비 점포당 매출 및 점포수 증강률 (단위 : %)> 구분 전체 대형마트 백화점 편의점 SSM 점포당 매출 증감률 13.0 4.7 14.2 1.3 △1.1 점포 수 증감률 6.9 △2.3 3.4 7.2 △1.1 온라인 유통업체 □ 온라인 유통업체 매출은 전년동월 대비 9.1% 증가하였으며, 도서/문구(△2.3%), 스포츠(△0.5%) 품목을 제외한 대부분 품목에서 매출이 상승 ㅇ 모임·실외활동 증가에 따른 화장품(18.1%) 및 가공식품·식음료 등 식품(17.9%) 수요증가, 여행·공연 예약상품 등 서비스/기타(13.6%) 품목의 판매호조 지속 <‘22년 6월 상품군별 전년동월 대비 매출증감률‧매출비중 (단위 : %)> 구분 전체 가전 전자 도서 문구 패션 의류 스포츠 화장품 아동 유아 식품 생활 가구 서비스기타 매출증감률 9.1 1.0 △2.3 6.0 △0.5 18.1 2.1 17.9 8.0 13.6 매출비중 100.0 20.5 1.7 9.9 3.7 4.7 3.4 24.2 15.5 16.4 참고 조사대상 및 유사통계 간 비교 【 (참고1) 매출동향 조사대상 】 □ 오프라인 유통업체(13개사) ∙ 백화점(3) : 롯데백화점, 현대백화점, 신세계백화점 ∙ 대형마트(3) : 이마트, 홈플러스, 롯데마트 ∙ 편의점(3) : 지에스25, 씨유, 세븐일레븐(바이더웨이 포함) ∙ 준대규모점포(SSM)(4) : 이마트에브리데이, 롯데슈퍼, 지에스더후레쉬, 홈플러스익스프레스 □ 온라인 유통업체(12개사) ∙ G마켓글로벌(G마켓‧옥션), 11번가, 인터파크, 쿠팡, SSG(이마트‧신세계), 에이케이몰, 홈플러스, 갤러리아몰, 롯데마트, 롯데온, 위메프, 티몬 ※ 유통업체별 협회(백화점·체인스토어·온라인쇼핑협회) 및 개별 유통업체(편의점)를 통해 조사 【 (참고2) 유사통계 간 비교 】 통계 명 주요 유통업체 (오프라인) 매출동향조사 서비스업동향조사 온라인쇼핑동향조사 작성기관 산업통상자원부 통계청 작성목적 소비동향 파악 서비스업‧도소매업 사업체의 경영실태 파악 온라인쇼핑동향 분석 모집단 주요 오프라인 유통업체 (13개사) 국내에서 서비스업을 운영하는 사업체 전체 연간거래액이 24백만원 이상인 온라인쇼핑 운영업체 (13,000여개) 표본추출틀 주요 오프라인 유통업체 (13개사) 2015 경제총조사 결과, 한국표준산업분류 대분류 13개 업종 공정위 PG사, 새올 행정시스템, 경총자료 조사대상 주요 오프라인 유통업체 13개사 (유의표본) 표본 17,300개 사업체 표본 1,100개 사업체 포괄범위 상품 및 서비스 거래금액 판매액(상품) 23개 상품군별 상품 및 서비스 거래금액 붙임 조사대상 유통업체별 매출 추이 □ 대형마트 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비 식품 식품 합계 가전/문화 의류 가정/생활 스포츠 잡화 기타 소계 ‘21. 6월 △15.2 △10.4 △15.3 △8.4 △29.4 0.0 △14.6 6.0 △2.4 7월 15.0 △3.5 △7.4 11.8 △4.1 △1.5 1.3 10.9 7.3 8월 △14.9 △19.1 △16.1 △13.6 △33.2 △10.8 △16.5 0.4 △5.5 9월 △5.5 △1.1 △14 5.1 △14.4 8.1 △8.6 △15.3 △13.3 10월 9.6 △1.5 △6.8 △10.4 △21.2 △5.4 △1.8 3.5 1.4 11월 △17.8 △1.8 △14.8 △13.7 △17.2 0.1 △13.6 △8.3 △10.3 12월 △6.1 7.9 △7.7 5.2 6.3 30.1 △2.3 △7.9 △6.1 ‘22. 1월 △2.7 13.1 13.5 6.4 10.6 16.9 6.8 16.9 13.8 2월 0.5 △20.5 △24.1 △13.3 △20.5 △7.1 △14.6 △28.7 △24.0 3월 △8.0 △17.8 △5.3 △13.9 △16.1 △4.4 △9.0 4.8 0.0 4월 △0.6 13.2 △2.7 1.8 10.8 5.3 1.3 2.3 2.0 5월 △9.7 9.0 △3.9 5.3 6.0 3.0 △3.1 △3.2 △3.0 6월 1.0 5.3 1.1 1.4 2.3 8.2 1.8 2.3 2.3 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 △8.1 △4.0 △5.1 △5.8 △5.5 △0.7 0.1 △3.0 0.4 0.2 △4.7 △5 △2.3 △3.2 0.3 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비 식품 식품 합계 가전/문화 의류 가정/생활 스포츠 잡화 기타 소계 ‘22. 2월 14.0 3.4 14.0 1.3 1.6 2.0 36.4 63.6 100 ‘22. 3월 11.0 3.5 12.7 1.3 1.8 2.1 32.4 67.6 100 ‘22. 4월 10.7 4.9 12.4 1.7 2.3 2.2 34.2 65.8 100 ‘22. 5월 11.7 5.3 13.0 2.0 2.5 2.4 36.9 63.1 100 ‘22. 6월 10.8 4.8 14.1 1.8 2.3 2.4 36.2 63.8 100 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 △1.8 △1.3 △11.5 △16.1 △9.7 △11.5 △7.3 2.9 △13.1 △2.8 △4.1 △5.0 △2.9 구매단가 △0.6 8.7 6.8 3.4 12.4 1.3 1.3 10.6 △12.5 2.9 6.4 2.1 5.3 점포당 매출 0.9 11.2 △5.5 △10.8 4.1 △7.5 △3.2 17.4 △22.2 5.5 3.9 △1.5 4.7 * '22.6월 1인당 구매단가 : 52,041원 (전년동월 49,406원) ** '22.6월 점포당 매출액 : 49.6억원 (전년동월 47.4억원) / ‘22.6월 점포 수 : 381개 □ 백화점 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비식품품목 식품 합계 잡 화 여성 정장 여성 캐주얼 남성 의류 아동 스포츠 가정 용품 해외유명 브랜드 소계 ‘21. 6월 △5.4 4.1 4.1 4.9 17.0 △0.5 31.5 12.9 10.8 12.8 7월 △9.2 △9.5 0.9 △0.6 16.5 16.5 18.8 9.5 △2.6 7.8 8월 △2.6 1.5 △6.8 4.5 24.8 25.6 18.6 14.3 4.5 13 9월 12.5 19.3 23.6 27 36.9 17.4 38.1 27.3 11.8 24.3 10월 5.0 7.7 5.4 12.8 19.6 22.2 39.4 21.5 16.9 21 11월 7.3 15 13.3 14.9 25.7 3 32.9 18.9 13.1 18.3 12월 30.6 36.1 48.6 40.5 55.3 14.6 42.8 37.7 28.3 36.5 ‘22. 1월 31.0 23.7 35.5 38.7 46.3 6.9 46.5 32.7 60.0 37.2 2월 3.2 13.8 1.9 10.8 11.9 9.3 32.5 17.4 △30.3 9.3 3월 △2.4 6.9 △2.7 3.8 12.6 △5.4 21.1 8.7 0.2 7.8 4월 14.7 19.2 22.2 21.2 33.4 6.8 22.5 20.0 10.4 19.1 5월 21.9 22.7 25.3 24.5 30.0 3.1 23.6 20.8 12.4 19.9 6월 14.4 17.8 17.3 18.7 27.4 10.6 19.6 18.1 16.2 18.2 * 자료 : 해외유명브랜드는 각사 분류 기준 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 1.0 △1.7 △0.2 △0.1 △19.9 △8.4 △5.0 △6.0 △9.8 31.2 21.5 14.6 24.8 24.1 17.6 19.1 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비식품품목 식품 합계 잡 화 여성 정장 여성 캐주얼 남성 의류 아동 스포츠 가정 용품 해외유명 브랜드 소계 ’22. 2월 9.7 6.7 5.3 3.4 10.3 16.4 37.3 89.2 10.8 100 ’22. 3월 9.4 8.2 6.2 4.1 11.5 13.4 36.4 89.1 10.9 100 ‘22. 4월 10.3 7.0 6.7 4.6 12.8 13.1 34.9 89.4 10.6 100 ‘22. 5월 12.0 6.8 6.8 4.5 12.4 13.2 33.4 89.0 11.0 100 ‘22. 6월 11.7 6.5 7.4 4.2 11.8 13.5 33.5 88.6 11.4 100 * 자료 : 해외유명브랜드는 각사 분류 기준 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 1.4 △8.1 △6.8 13 7.1 7.5 29.6 21.2 △1.5 △7.2 7.8 11.4 9.8 구매단가 11.2 17.3 21.2 10 13 10.1 5.3 13.3 10.9 16.1 10.4 7.6 7.7 점포당 매출 10.8 5.9 9.2 18.1 15 12.4 29.7 30.4 5.6 4.2 15.1 15.9 14.2 * '22.6월 1인당 구매단가 : 114,201원 (전년동월 106,057원) ** '22.6월 점포당 매출액 : 413.3억원 (전년동월 361.8억원) / ‘22.6월 점포 수 : 60개 □ 편의점 ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비 식품품목 식품 합계 생활용품 잡화 담배 등 기타 소계 음료 등 가공 즉석 (신선일부) 소계 ‘21. 6월 △3.5 △6.0 3.4 2.6 10.0 4.8 9.1 6.0 7월 △9.0 △10.9 1.4 0.2 16.2 0.1 13.3 7.0 8월 △6.1 △9.4 2.1 1 9.1 △0.6 7.4 4.5 9월 11.5 △6.1 6 6.1 14.1 △0.3 11.5 9 10월 11.4 10.6 4.5 5.2 14.9 0.1 12.3 9 11월 7.9 9.7 5.9 6.1 8.8 △0.1 7.2 6.7 12월 21.6 11.0 8.9 9.9 8.8 4.5 8.1 8.9 ‘22. 1월 13.7 8.3 6.4 7.0 12.4 4.8 11.2 9.3 2월 4.8 3.8 9.2 8.7 7.1 1.9 6.3 7.4 3월 7.3 5.1 14.5 13.7 10.6 4.5 9.5 11.5 4월 11.1 3.1 8.9 8.9 13.6 8.2 12.7 10.9 5월 10.7 △1.3 10.6 10.2 14.8 12.2 14.3 12.5 6월 19.9 11.6 7.0 8.1 10.0 4.7 9.1 8.6 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3.9 2.9 5.2 4.1 3.4 0.5 2.8 2.9 2.4 5.1 7.2 7.1 8.2 6.8 9.5 10.6 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비 식품품목 식품 합계 생활용품 잡화 담배 등 기타 소계 음료 등 가공 즉석 (신선일부) 소계 ‘22. 2월 3.4 1.3 42.4 47.1 44.8 8.1 52.9 100.0 ‘22. 3월 3.3 1.2 44.2 48.7 42.9 8.4 51.3 100.0 ‘22. 4월 3.4 1.1 41.3 45.8 45.4 8.8 54.2 100.0 ‘22. 5월 3.6 1.2 40.5 45.3 45.9 8.9 54.7 100.0 ‘22. 6월 3.9 1.2 40.1 45.2 45.8 9.0 54.8 100.0 ㅇ 구매건수 및 구매단가 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 0.1 △1.6 △2.9 2.8 0.3 0.7 7.2 6.6 △0.1 2.5 7.2 12.6 5.5 구매단가 5.9 8.8 7.6 6.1 8.6 6 1.5 2.5 7.5 8.8 3.4 △0.1 3.0 * ‘22.6월 1인당 구매단가 : 6,645원 (전년동월 6,451원) ㅇ 점포당 매출액 증감률 추이 및 점포수 현황 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 점포증가율 6.2 6.3 6.4 6.3 6.2 5.7 5.8 5.9 5.9 6.3 6.5 6.9 7.2 점포당매출액 △0.2 0.7 △1.8 2.5 2.6 0.9 2.9 3.2 1.5 4.9 4.1 5.2 1.3 * ‘22.6월 점포당 매출액 : 5,279.2만원 (전년동월 5,209.9만원) / ’22.6월 점포 수 : 44,180개 □ 준대규모점포(SSM) ㅇ 전년동월 대비 상품군별 매출증감률 추이 (단위 : %) 구분 비식품 식품품목 합계 일상용품 생활잡화 소계 농수축산 신선·조리식품 가공식품 소계 ‘21. 6월 △11.7 △7.6 △9.9 △1.3 △4.4 0.5 △1.5 △2.4 7월 △12.9 △2.9 △8.6 2.5 7.5 3.9 4.2 2.8 8월 △18.9 △5.7 △13.2 △4.4 △7.2 △2.3 △4.4 △5.3 9월 △14.9 △8.1 △11.9 △16.7 △17.3 △15.6 △16.6 △16.1 10월 △12 △0.2 △6.8 0.8 △3 △1.5 △1 △1.6 11월 △13.9 △5.7 △10.2 △6.3 △5.5 △5.7 △5.9 △6.3 12월 △13.9 △3.5 △9.1 △14.3 △11.6 △10.6 △12.5 △12.2 ‘22. 1월 0.3 4.7 2.1 △4.0 △4.2 5.2 △1.5 △1.2 2월 △10.2 △3.0 △7.2 △16.2 △2.0 △2.3 △8.5 △8.4 3월 △4.4 1.3 △2.0 2.3 4.6 11.1 5.3 4.6 4월 △3.3 △3.8 △3.5 △4.5 △1.9 3.4 △1.6 △1.8 5월 △5.1 △1.7 △3.7 △5.6 △2.7 1.7 △2.8 △2.8 6월 △6.9 △4.3 △5.8 △5.1 △2.0 3.6 △1.8 △2.2 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 0.3 △2.0 △3.6 △1.5 2.1 △10.0 1.6 △6.1 △4.8 △13.9 △5.6 △7.4 △7.0 △9.1 △1.5 △2.3 ㅇ 상품군별 매출 비중 (단위 : %) 구분 비식품 식품품목 합계 일상용품 생활잡화 소계 농수축산 신선·조리식품 가공식품 소계 ‘22. 2월 5.2 4.1 9.3 37.9 25.2 27.7 90.7 100.0 ‘22. 3월 4.9 3.7 8.6 40.5 24.8 26.1 91.4 100.0 ‘22. 4월 5.1 3.8 8.9 40.0 24.9 26.3 91.1 100.0 ‘22. 5월 5.3 4.1 9.4 39.1 25.1 26.4 90.6 100.0 ‘22. 6월 5.5 4.1 9.5 38.0 25.8 26.6 90.5 100.0 ㅇ 구매건수ㆍ구매단가 및 점포당 매출액 증감률 추이 (단위 : %) 증감률 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 구매건수 △5.6 △3.3 △8.1 △14 △6.3 △9 △10.5 △4.8 △7.0 1.0 △2.1 △2.0 △4.4 구매단가 3.4 6.4 3 △2.5 5 2.9 △1.9 3.8 △1.5 3.6 0.3 △0.8 2.3 점포당 매출 4.0 8.1 △1.1 △12.8 1.8 △3.8 △9.5 0.2 △7.7 5.5 △1.0 △2.1 △1.1 * '22.6월 1인당 구매단가 : 16,610원 (전년동월 16,232원) ** '22.6월 점포당 매출액 : 3.50억원 (전년동월 3.54억원) / ‘22.6월 점포 수 : 1,095개 □ 온라인 유통 ㅇ 전년동월 대비 매출증감률 추이 (단위 : %) 2021년 2022년 6월 7월 8월 9월 10월 11월 12월 1월 2월 3월 4월 5월 6월 19.6 20.2 11.1 14.5 19.7 14.8 12.8 9.1 14.2 7.9 11.0 11.0 9.1 ㅇ 전년동월 대비 매출증감률 추이 (단위 : %) 구분 가전/ 전자 도서/ 문구 패션/ 의류 스포츠 화장품 아동/ 유아 식품 생활/ 가구 서비스/ 기타 합계 ‘21. 6월 3.8 17.7 1.3 △0.9 19.0 △2.7 40.0 6.5 85.7 19.6 7월 30.6 2.3 2.0 △4.8 14.9 △0.6 30.7 4.4 44.9 20.2 8월 4.6 3.2 △1.4 5.1 20.3 △4.6 28.2 4.5 17 11.1 9월 9.6 2.0 4.9 8.4 19.9 △0.6 17.1 9.7 44.9 14.5 10월 22.7 12.5 4.9 5.6 16.2 0.2 25.3 13.4 46.1 19.7 11월 14.6 △1.2 6.3 1.4 19 2.7 19.9 7.3 36.4 14.8 12월 3.9 △4.5 14.3 2.1 17.4 1.5 8.0 26.9 30.3 12.8 ‘22. 1월 △4.2 △9.1 14.6 0.9 24.2 △1.8 18.0 4.3 23.3 9.1 2월 17.0 2.5 7.4 5.0 23.7 4.7 9.8 12.1 26.8 14.2 3월 1.4 0.4 △2.7 △1.4 15.9 5.0 24.6 8.4 1.9 7.9 4월 △0.5 3.9 14.9 △0.6 18.6 5.4 18.1 6.6 24.0 11.0 5월 3.8 2.3 11.9 10.7 26.7 4.5 17.7 3.7 17.6 11.0 6월 1.0 △2.3 6.0 △0.5 18.1 2.1 17.9 8.0 13.6 9.1 ㅇ 전년동기 대비 매출증감률 추이 (단위 : %) 2019년 연 간 2020년 연 간 2021년 연 간 2022년 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 3분기 4분기 1분기 2분기 14.6 13.8 12.6 14.2 19.8 15.4 17.8 20.4 18.4 14.3 17.9 15.2 15.6 15.7 10.2 10.4 ㅇ 상품군별 매출 비중 (단위 : %) 구분 가전/ 전자 도서/ 문구 패션/ 의류 스포츠 화장품 아동/ 유아 식품 생활/ 가구 서비스/ 기타 합계 ‘21. 6월 22.1 1.9 10.2 4.0 4.3 3.6 22.4 15.7 15.8 100.0 7월 24.2 1.9 9.0 4.0 4.3 3.7 22.6 15.4 14.8 100.0 8월 23.3 2 7.5 3.6 4.5 3.7 24.8 15.7 14.9 100.0 9월 22.3 2 8.8 3.9 4.6 3.6 25.6 15.9 13.4 100.0 10월 24.1 1.9 11 4.3 4.4 3.6 21.7 15.6 13.4 100.0 11월 25.1 1.9 11.2 3.9 4.4 3.5 21.1 15.1 13.9 100.0 12월 21.5 2.4 10.3 3.3 4.3 4.6 22.0 18.5 13.0 100.0 ‘22. 1월 21.5 2.1 8.5 2.8 5.0 3.4 27.6 15.0 13.9 100.0 2월 25.3 2.1 7.8 2.7 4.7 3.5 23.1 15.5 15.3 100.0 3월 20.6 2.4 9.3 3.1 4.5 3.6 25.6 15.7 15.1 100.0 4월 19.9 2.1 10.5 3.8 4.8 3.9 24.3 15.2 15.4 100.0 5월 21.7 1.7 10.1 4.0 5.0 3.7 23.5 14.8 15.5 100.0 6월 20.5 1.7 9.9 3.7 4.7 3.4 24.2 15.5 16.4 100.0 ※ 상기 [조사대상 유통업체별 매출 추이]는 동 조사에 협조하는 주요 유통업체별 회계ㆍ정산 과정에서 수정이 있을 시 차기 보도자료에 반영함에 따라, 일부 차이가 발생할 수 있음

닫기

-

0728(29조간)유통물류과, '22년 상반기 및 6월 주요유통업체 매출동향.pdf

미리보기

-

2025년도 반도체 분야 신규 지원대상 연구개발과제 공고 2025-01-17

산업통상자원부 공고 제2025-046호 2025년도 반도체 분야 신규 지원대상 연구개발과제 공고 2025년도 반도체분야 신규 지원대상 연구개발과제를 다음과 같이 공고하오니수행하고자 하는 자는 신청하여 주시기 바랍니다.2025년 1월 17일산업통상자원부장관

>알림·뉴스>사업공고

-

2025년도 반도체 분야 신규 지원대상 연구개발과제 공고.hwpx

미리보기

미리보기

산업통상자원부 공고 제2025-046호 2025년도 반도체 분야 신규 지원대상 연구개발과제 공고 2025년도 반도체분야 신규 지원대상 연구개발과제를 다음과 같이 공고하오니 수행하고자 하는 자는 신청하여 주시기 바랍니다. 2025년 1월 17일 산업통상자원부장관 < 목 차 > 1. 사업개요 1-1. 사업목적 및 지원대상 분야 1-2. 연구개발비 지원 규모 및 기간 2. 사업추진체계 3. 연구개발비 지원기준 및 기술료 징수기준 3-1. 연구개발비 지원기준 3-2. 기술료 징수 여부 및 방법 3-3. 연구개발비 산정시 유의사항 4. 지원분야 및 신청자격 등 4-1. 지원분야 4-2. 신청자격 4-3. 지원제외 처리기준 5. 평가 절차 및 기준 5-1. 평가절차 5-2. 평가기준 6. 근거법령 및 규정 7. 신청방법, 신청서 제출기한 및 접수처 8. 제출 서류 사항 9. 기타 지원 내용 및 유의 사항 10. 문의처 등 1. 사업개요 1-1. 사업목적 ◦미래 우리나라의 먹거리가 될 새로운 산업 창출과 생태계 조성을 위한 핵심기술 개발 - 시장선도를위한한국주도형K-센서기술개발, 신시장창출을위한수요연계시스템반도체기술개발, 산업현장맞춤형온디바이스AI반도체기술개발, 화합물전력반도체고도화기술개발, 반도체첨단패키징선도기술개발, 민관공동투자반도체고급인력양성, PIM인공지능반도체핵심기술개발 1-2. 연구개발비 지원 규모 및 기간 세부사업명 공고예산 (백만원) 지원과제 (개) 양식교부 및 접수처 지원기간 및 지원규모 시장선도를위한한국주도형 K-Sensor기술개발 731 1 범부처통합연구지원시스템 (iris.go.kr) 연구개발과제별 특성에 따라 달리함 * 첨부파일(붙임 01. 신규지원 대상 연구개발과제 안내문) 참조 신시장창출을위한수요연계시스템반도체기술개발 1,500 1 산업현장맞춤형 온디바이스AI반도체기술개발 4,320 4 화합물전력반도체고도화기술개발 5,500 5 반도체첨단패키징선도기술개발 17,800 16 민관공동투자반도체고급인력양성 4,597 22 PIM인공지능반도체핵심기술개발 2,000 2 ◦신규 연구개발과제 선정 시 협약 기간은 해당 연구개발과제의 전체 연구개발기간에 대해 일괄로 체결하며, 연구개발과제의 특성을 고려해 1년에서 4년 단위로 단계를 구분할 수 있음. 2. 사업추진체계 ◦추진체계 (일반형) 산업통상자원부 사업심의위원회 전 문 기 관 (한국산업기술기획평가원) 연구개발과제평가단 주관연구개발기관 (연구책임자) … 공동연구개발기관 1 (공동연구책임자) 공동연구개발기관 2 (공동연구책임자) … 공동연구개발기관 N (공동연구책임자) ◦추진체계 (통합형/병렬형) 산업통상자원부 사업심의위원회 전 문 기 관 (한국산업기술기획평가원) 연구개발과제평가단 총괄주관연구개발기관 (총괄연구책임자) … 세부주관 연구개발기관1 (세부연구책임자) 세부주관 연구개발기관2 (세부연구책임자) … 세부주관 연구개발기관N (세부연구책임자) 공동연구 개발기관1 (공동연구 책임자1) 공동연구 개발기관N (공동연구 책임자N) 공동연구 개발기관1 (공동연구 책임자1) 공동연구 개발기관N (공동연구 책임자N) … 공동연구 개발기관1 (공동연구 책임자1) 공동연구 개발기관N (공동연구 책임자N) - “주관연구개발기관”이라 함은 해당 연구개발과제를 주도적으로 수행하는 기관 - “공동연구개발기관”이라 함은 해당 연구개발과제에 참여하여 주관연구개발기관과 공동으로 수행하는 기관 - “연구책임자”라 함은 해당 연구개발과제를 총괄하여 수행하는 책임자 - “과제참여자(책임자 및 연구원 등)”는 해당 과제에 실질적 참여자로 국한 할 것 3. 연구개발비 지원기준 및 기술료 징수기준 3-1. 연구개발비 지원기준 □ 정부지원연구개발비 지원 및 기관부담연구개발비 부담 조건 ① 공통사항 ◦연구개발과제의 연구개발비는 정부지원연구개발비와 기관부담연구개발비, 그 외 기관·단체·개인이 지원하는 연구개발비(지방자치단체 등이 보유한 현금 및 현물)로 구성 ◦연구개발기관 중 영리기관의 경우 기관부담연구개발비 중 현금을 개별 부담하여야 함 - 수요기업*의 경우 정부지원연구개발비 지원 없이 참여가 가능하며 이 경우 기관부담연구개발비 중 현물(참여연구자 인건비 등)로 구성할 수 있음 * ‘수요기업’이란 개발제품 및 기술에 대한 구매 또는 실시를 희망하여 개발과정에서 성능 평가 및 검증 역할을 하는 참여기업임 ◦ 연구개발비 구성 시 수요기업, 과제 특징(초고난도과제, 챌린지 트랙, 대형통합형, 서비스형, 국제공동연구개발과제 등), 핵심전략기술 관련 기술개발 등 유리한 조건 적용 가능 (단, 중복 적용 불가) ② 정부지원연구개발비 지원 기준 ㅇ 정부지원연구개발비 지원비율은 아래의 표와 같이 연구개발기관 및 연구개발과제 유형에 따라 달리 적용 가능 - 수요기업으로 참여하는 공동연구개발기관은 기업 유형에 관계없이 중소기업 수준으로 정부지원연구개발비를 지원할 수 있음. 단, 연구개발과제평가단 심의를 거쳐 수요기업이 아니라고 판단될 경우 연구개발기관 유형에 따라 연구개발비를 재산정하여야 함 - 산업위기지역 소재기업* 중, 중소기업이 수행하는 연구개발과제는 예외적으로 정부지원연구개발비 지원비율을 해당 연구개발기관 연구개발비의 80% 이하로, 중견기업이 수행하는 혁신제품형 연구개발과제는 65% 이하로 할 수 있음 * ‘산업위기지역 소재기업’이란, 「지역 산업위기 대응 및 지역경제 회복을 위한 특별법」제8조제2항, 제9조제2항, 제10조제6항 및 제8항, 제13조와 같은 법 시행령 제6조제3항, 제7조제4항, 제8조제3항 및 제6항에서 위임한 사항과 그 시행에 관하여 필요한 사항을 규정하기 위해 산업통상자원부에서 고시한 “지역 산업위기대응 제도의 지정기준 등에 관한 고시”에 따라 지정된 산업위기대응특별지역의 주된 산업에 종사하는 기업임(지정 기간에 한함) 연구개발기관1) 유형 연구개발과제 유형 원천기술형 혁신제품형 중소·중견기업이 아닌 기업 해당 연구개발기관 연구개발비의 50% 이하 해당 연구개발기관 연구개발비의 33% 이하 중견기업2) 해당 연구개발기관 연구개발비의 70% 이하 해당 연구개발기관 연구개발비의 50% 이하 중소기업3) 해당 연구개발기관 연구개발비의 75% 이하 해당 연구개발기관 연구개발비의 67% 이하 그 외 해당 연구개발기관 연구개발비의 100% 이하 해당 연구개발기관 연구개발비의 100% 이하 1) ‘연구개발기관’이란 과제수행을 위하여 선정된 주관연구개발기관 및 공동연구개발기관임 2) ‘중견기업’이란 「중견기업 성장촉진 및 경쟁력 강화에 관한 특별법」제2조 1호의 기업임 * 단, 「중견기업 성장촉진 및 경쟁력 강화에 관한 특별법」시행령 제7조에 따라 산정한 평균매출액 등이 3천억원 미만인 중견기업은 중소기업 수준으로 정부지원연구개발비 지원 가능 3) ‘중소기업’이란 「중소기업기본법」제2조제1항에 따른 기업임 ◦ ‘붙임 01. 신규지원 대상 연구개발과제 안내문(첨부 참조)’ 중 과제 특징이 ‘초고난도, 혁신도전R&D, 챌린지 트랙, 대형통합형, 서비스형, 국제공동연구개발과제‘에 해당할 경우 과제 유형과 상관없이 원천기술형 기준으로 연구개발비를 산정할 수 있음 ③ 기관부담연구개발비 중 현금부담비율 기준 ㅇ 연구개발기관에서 부담하여야할 기관부담연구개발비 중 현금부담비율은 아래의 표와 같이 연구개발기관 유형에 따라 달리 적용 가능 - 수요기업으로 참여하는 공동연구개발기관,「중견기업 성장촉진 및 경쟁력 강화에 관한 특별법」시행령 제7조에 따라 산정한 평균매출액 등이 3천억원 미만인 중견기업은 기업 유형에 관계없이 중소기업 수준으로 현금부담 비율을 적용할 수 있음 (단, 연구개발과제평가단 심의를 거쳐 수요기업이 아니라고 판단될 경우 연구개발기관 유형에 따라 연구개발비를 재산정하여야 함) 연구개발기관 유형 기관부담연구개발비 현금부담비율 연구개발과제 유형 : 원천기술형/ 혁신제품형(공통) 중소·중견기업이 아닌 기업 해당 연구개발기관 기관부담연구개발비의 15% 이상 중견기업 해당 연구개발기관 기관부담연구개발비의 13% 이상 중소기업 해당 연구개발기관 기관부담연구개발비의 10% 이상 그 외 필요시 부담 ◦국외기관(기업, 대학 및 연구소 등)의 경우는 위 표에서 ‘그 외’를 적용함 ④ 「산업기술혁신사업 공통 운영요령」제24조제2항 및 제25조제4항의 “핵심전략기술* 관련 기술개발에 참여하는 기업”은 기관 유형에 관계없이 중소기업 수준으로 정부지원연구개발비의 지원 및 기관부담연구개발비 중 현금을 부담할 수 있음. 신청과제의 참여기업은 ‘3-1. 연구개발비 지원기준’ ②항 및 ③항 기준으로 연구개발계획서를 우선 신청하며, 선정평가 결과 ‘지원대상’으로 선정된 경우 협약 체결 이후 신청기업에 한하여 별도 위원회 심의를 거쳐 「산업기술혁신사업 공통 운영요령」 제24조제2항 및 제25조제4항의 “핵심전략기술 관련 기술개발에 참여하는 기업”**에 해당 여부를 확정하여 지원비율을 협약 시 변경할 수 있음 * 「핵심전략기술 및 핵심전략기술과 관련된 품목, 핵심전략기술 선정・재검토 세부절차 등에 관한 고시」제4조제1항에 따른 [별표] 핵심전략기술 목록 참조 ** 핵심전략기술 관련 기술개발에 참여하는 기업에 대한 정부지원연구개발비 지원기준은 「산업기술혁신사업 공통 운영요령」제27조(협약의 변경)에 따라 적용함 3-2. 기술료 등 징수 기준 □ 기술료 징수 대상 및 기준 ◦기술료 등 징수 대상 -‘기술료 징수 및 관리에 관한 통합요령 제3조 제6호에 따른 ’기술료등납부의무기관’은 실시계약을 체결하고 기술료를 징수하거나, 직접 연구개발성과를 실시하는 경우 기술료를 납부해야 함 - 국외기관은 국내기관에 성과를 이전하기로 하는 경우, 정부납부기술료를 면제하는 것을 원칙으로 함. 단, 국내법인의 지사인 경우 국내기관과 같은 기준으로 처리함. * 상기내용이 해당하는 경우 국제공동계약에 관련 내용을 반영하여야 함 ◦기술료 상한 연구개발기관 유형 중소기업인 경우 중견기업인 경우 중소·중견기업이 아닌 기업 기술료 상한 정부지원 연구개발비의 10% 정부지원 연구개발비의 20% 정부지원 연구개발비의 40% □ 기술료 산정기준 및 납부기한 ① 기술료 산정 기준 연구개발기관 유형 중소기업인 경우 중견기업인 경우 중소·중견기업이 아닌 기업 ① 실시계약 체결한 경우 실시기관으로부터 징수한 기술료의 2.5% 실시기관으로부터 징수한 기술료의 5% 실시기관으로부터 징수한 기술료의 10% ② 직접 실시할 경우 (수익금액X기술기여도)의 2.5% (수익금액X기술기여도)의 5% (수익금액X기술기여도)의 10% ※ ‘기술기여도’는 선정된 과제에 대해 협약시 정하며, 직접 기술실시를 한 날이 속하는 해의 다음 해 6월30일까지 매년 재무제표 및 재고자산수불부 등 매출액 관련 자료를 제출해야 함 ② 기술료 납부 기한 ㅇ 연구개발성과소유기관이 실시기관과 기술실시계약 체결하고 기술료를 징수할 경우 - 처음 기술료를 징수한 날이 속한 해의 다음 해부터 5년이 되는 날 또는 연구개발과제가 종료된 날부터 7년이 되는 날 중 먼저 도래하는 날까지 납부 ㅇ 연구개발성과소유기관이 직접 실시할 경우 -직접실시로 수익이 처음 발생한 날이 속하는 해의 다음 해부터 5년이 되는 날 또는 연구개발과제가 종료된 날부터 7년이 되는 날 중 먼저 도래하는 날까지 매년 수익이 발생한 해마다 납부해야 함 3-3. 연구개발비 산정시 유의사항 □ 영리기관 소속 참여연구원의 인건비는 현물계상이 원칙이나 다음 기준에 따라 현금으로 산정 가능 ◦영리기관의 경우, 해당 연구개발과제 수행을 위해 신규로 채용하는 연구자의 인건비계상률에 따른 인건비를 현금으로 산정할 수 있음 - 사업공고일 기준 6개월 이전(2024년 7월 17일)부터 각 연구개발과제 종료 시점 사이에 채용한 연구원은 전체 연구개발기간에 걸쳐 신규인력으로 간주하며, 신규 참여연구자 인건비 금액만큼 기존 참여연구자의 인건비 현금 산정 가능. ◦ 창업초기 중소기업(사업개시일로부터 연구개발기간 시작일까지 7년이 지나지 아니한 중소기업) 소속 기존인력의 인건비 현금 산정 가능 ◦「산업기술혁신사업 공통운영요령」별표 제4호의 인건비 현금 인정 분야의 연구개발과제를 수행하는 영리기관 소속 연구자의 인건비계상률에 따른 인건비 <인건비 현금 인정 분야의 구체적 산정기준> ◇ 연구개발과제의 전체 연구내용이 지식서비스, 소프트웨어 및 설계기술 등 인건비 현금 인정 분야에 해당되는 경우에는, - 중소·중견기업인 연구개발기관(주관연구개발기관 또는 공동연구개발기관)은 연구개발계획서 표지에 해당 기술분류 코드번호를 기입하고 소속 연구자의 인건비를 현금으로 산정가능 ◇ 또한, 주관연구개발기관 및 공동연구개발기관 중 어느 하나만 지식서비스, S/W 및 설계기술 등에 해당되는 경우에도 해당 중소·중견기업 소속 연구자의 인건비는 현금으로 산정가능 - (예시) 주관연구개발기관의 연구개발내용은 자동차 차체 및 경량화 기술에 속하고, 공동연구개발기관의 연구개발내용은 자동차관련 소프트웨어 개발인 경우에, 공동연구개발기관의 연구개발내용만 인건비 현금 인정 분야에 속함. 따라서, 중소·중견기업인 공동연구개발기관은 해당 코드번호(100212, 자동차/철도차량 관련 IT·SW)를 연구개발계획서 표지에 기입하고, 참여연구자의 인건비를 현금으로 산정가능 ◇ 단, 인건비 현금 인정분야로 신청된 경우라 하더라도 평가단에서 인정하지 않는 경우 현금으로 산정할 수 없음 ◇ 인건비 현금인정 분야에 대한 자세한 내용은 「산업기술혁신사업 공통운영요령」 [별표4]을 참조하고, 해당 기술분야에 대한 코드번호는 「산업기술혁신사업 공통 운영요령」 [별표1]을 참조 ◦ 「연구산업진흥법」제2조 제1호 가목 및 나목의 산업을 영위하는 사업자 중 동법 제6조 제1항에 따른 전문연구사업자로 신고된 연구개발기관 소속 참여연구자의 인건비(단, 연구개발기간 시작일 이전 신고한 경우에 한하며, 연구개발과제가 단계로 구분된 경우 해당 단계 시작일을 기준으로 함) ◦육아부담으로 시간선택제(통상 근무시간보다 짧은 시간으로 주당 15~35시간 범위에서 정한 시간을 근무하는 것)로 근무하는 영리기관 소속 여성연구자의 인건비 현금계상 가능 ◦ 「산업디자인진흥법」제9조, 동법 시행규칙 제9조에 따른 산업디자인전문회사가 해당분야 연구개발과제에 참여할 경우 그 기업 소속 참여연구자의 인건비 현금계상 가능 ◦ 산업위기지역에 소재한 영리기관의 경우, 정부지원연구개발비의 50% 이내로 해당기업 참여연구자의 인건비계상률에 따른 인건비 현금계상 가능 ◦ 국제공동과제의 경우, 인력교류 협력을 위해 연구인력 파견 비용을 연구활동비에 계상 가능 □ 청년인력 추가채용 혜택 (연구개발기관 중 기업만 해당) ㅇ청년인력(채용시점 기준 만 34세 이하, 군 복무 기간만큼 월 단위로 계산(1개월 미만은 올림)하여 추가로 인정하되 최대 만 39세까지 한정) 일자리 창출을 위해 참여기업이 전체연구개발기간 동안 채용할 인원수(기본채용 인원*)를 초과하여 청년인력을 신규채용하는 계획을 연구개발기간 개시 시점에 제시하거나 계획하지 않았더라도 연구개발기간 중 실제 채용한 경우, 추가채용인력의 해당 연도 인건비 액수만큼 해당 연도 기관부담연구개발비 현금을 감액하고 동액 상당의 현물을 추가로 부담할 수 있음. 이때, 기관부담연구개발비 현금을 납부한 경우 기관부담연구개발비 현금의 감액 범위는 해당 연구개발기관이 추가 채용 사실을 소명하여 감액 승인을 요청한 시점의 연구개발비 현금 잔액을 한도로 함. * 기본채용 인원 : 전체 연구개발기간에 걸친 각 참여기업의 정부지원연구개발비 합계액(계획금액 기준)이 5억원 이상인 경우 청년인력은 1차년도에 1명 이상 배정하여야 하며, 정부지원연구개발비 합계액이 5억원의 배수에 달할 때마다 해당 연도 말까지 채용하여야 할 인원을 1명씩 가산 예시) 연구개발기관 중 3개의 기업이 나누어 받는 총 정부지원연구개발비 13.8억원인 경우, 참여기업의 연차별 기본채용 인원수 구분 1차년도 2차년도 3차년도 해당연도 누적 해당연도 누적 해당연도 누적 정부지원연구개발비 3.8억 3.8억 5억 8.8억 5억 13.8억 기본채용 인원 1명 1명 1명 2명 0명 2명 □ 참여연구원 출산전후 휴가기간 인건비 지급 허용 ㅇ참여연구원의 출산전후휴가 기간 동안에도 연구개발기관이 해당 연구원에 대하여 지급 의무를 부담하는 급여(고용보험법 등에 따라 정부에서 지원받을 수 있는 액수는 제외)는 인건비로 계상·집행 가능 □ 영리기관 대상 연구지원전문가 지원제도 ㅇ영리기관에서 과제 지원을 위해 한국산업기술기획평가원에서 실시하는 소정의 연구지원전문가 교육을 수료할 경우(단, 연구지원전문가 교육 수료일이 포함된 해당 월부터 인건비 지급 가능), 1명에 한해 연구개발비 중 간접비에서 해당 인력의 인건비를 현금 산정할 수 있음 - 신규채용인력은 사업공고일 기준 6개월 이전(2024년 7월 17일)부터 채용한 경우에 인정 - 기존인력은 해당인력 인건비의 50%까지 현금으로 산정 가능(타 과제 포함 실제 급여총액의 50%를 초과할 수 없음) □ 학생연구원 연구몰입을 위한 연구근접지원인력 활용 ㅇ대학의 경우 연구책임자(교수 등) 기준으로 산업부 소관 국가연구개발사업으로 지원받는 연차별 정부지원연구개발비 합계가 5억원 이상일 경우 연구비 관리 등 연구행정 지원을 위한 연구근접지원인력을 1명 이상 활용하여야 함 - 연구근접지원인력 인건비는 관리과제 중 1개에 100% 산정하거나, 각 관리과제에 나누어 산정하는 방식으로 직접비에서 활용 가능 - 학생연구원 등 참여연구원에게 연구비 관리업무를 할당하고 연구근접지원인건비를 계상하는 것도 가능 * 이 경우 기관 내 학생인건비 지급기준의 50% 이상 계상 필요 □ 참여연구원 중 박사후연구원에게 인건비를 지급한 경우에는 연구개발비 정산 시 근로계약서를 반드시 제출하여야 함 □ 비영리 연구개발기관의 당해연도 직접비 집행비율이 50% 이하인 경우, 간접비 집행비율 중 직접비 집행비율을 초과하는 부분은 반납하여야 함 □ 외주 용역비는 연구개발과제의 핵심공정·기술개발에 해당하지 않는 경우에 한하며, 연구개발내용의 일부를 연구개발기관이 아닌 제3자에게 위탁하는 용도로 산정할 수 있다. 이때, 3,000만원(부가가치세 포함) 이상 외주 용역의 경우 협약 시 또는 다음단계 연구개발기간 시작시 연구개발계획서에 해당 용역의 내역 및 금액을 명시하여야 한다. □연구개발과제별 안전관리 강화 ◦지원대상 과제 중 별도의 위원회를 통해 「산업기술혁신사업 공통 운영요령」 제2조 제1항 제40의3호에 따른 “안전관리형 과제”로 지정되는 경우, 관련 규정에 따라 ‘과제별 안전관리계획’을 제출하고 적절한 안전조치 및 점검을 실시하여야 함 ◦연구실 안전관리비 산정 : 간접비 내에 인건비 합계의 1%이상에 해당하는 금액을 「연구실 안전환경 조성에 관한 법률 시행규칙」 제13조(안전 관련 예산의 배정)에 따른 연구실 안전관리비로 책정하여야 함 * 대학, 국·공립연구기관, 과학기술분야 정부출연연구기관, 특정연구기관에 한함 4. 지원분야 및 신청자격 등 4-1. 지원분야 ◇ 연구개발과제는 유형별로 3가지 항목(가~다)으로 분류되며, 각 항목별 1개 이상 해당함 구분 연구개발과제유형 가. 추진체계 나. 개발형태 다. 공모형태 A과제 일반형 혁신제품형 지정공모형 통합형 원천기술형 품목지정형 병렬형 □ 연구개발과제 유형 - 가 (추진체계) ◦일반형 : 총 1개 연구개발과제로 구성되어 주관연구개발기관과 공동연구개발기관이 공동으로 수행하는 연구개발과제 -“주관연구개발기관”이라 함은 연구개발과제를 주관하여 수행하는 기관(기업 포함) -“공동연구개발기관”이라 함은 해당 연구개발과제에 참여하여 주관연구개발기관과 공동으로 과제를 수행하는 기관(기업 포함) -”연구책임자”라 함은 해당 연구개발과제를 총괄하여 수행하는 책임자 ◦통합형 : 세부연구개발과제의 기술개발결과가 상호연계되어 사업화 또는 상품화되는 과제로 총괄연구개발과제, 세부연구개발과제의 컨소시엄으로 구성하여 수행하는 연구개발과제(과제 신청 시 총괄연구개발과제 및 세부연구개발과제 간 협의를 통하여 전체 컨소시엄을 구성) ◦병렬형 : 세부연구개발과제의 기술개발 결과가 독립적으로 사업화 또는 상품화가 가능하면서 상호연계도 가능한 연구개발과제로 총괄연구개발과제, 세부연구개발과제가 평가 후 컨소시엄으로 구성되어 수행하는 연구개발과제(총괄연구개발과제 및 세부연구개발과제는 각각 단독으로 신청하여 경합평가 후 선정된 연구개발과제들이 협약을 통해 컨소시엄을 구성) -“총괄주관연구개발기관”이라 함은 연구개발과제가 총괄연구개발과제 및 세부연구개발과제로 구분되는 경우에 총괄연구개발과제의 관리를 수행하는 주관연구개발기관 -“세부주관연구개발기관”이라 함은 연구개발과제가 총괄연구개발과제 및 세부연구개발과제로 구분되는 경우에 세부연구개발과제를 주도적으로 수행하는 주관연구개발기관 -“총괄연구책임자”라 함은 연구개발과제가 총괄연구개발과제 및 세부연구개발과제로 구분되는 경우에 총괄주관연구개발기관에 소속되어 연구개발과제 전체를 관리하는 연구책임자 □ 연구개발과제 유형 - 나 (개발형태) ◦원천기술형 : 제품에 적용 가능한 독창적․창의적인 원천기술을 개발하는 연구개발과제의 유형 ◦혁신제품형 : 산업원천기술을 접목한 제품을 개발하는 연구개발과제의 유형 □ 연구개발과제 유형 - 다 (공모형태) ◦지정공모형 : 개발이 필요한 대상기술과 도전적 기술목표(RFP)를 제시 ◦품목지정형 : 필요 기술의 구체적 스펙(RFP) 제시 없이 품목(제품, 제품군)만 제시(지정공모와 자유공모의 중간 형태) □ 지원대상 연구개발과제 목록 ◦RFP/품목서는 첨부파일(붙임 01. 신규지원 대상 연구개발과제 안내문)을 참조 세부사업명 내역사업명 PD 분야 공고 예산 (백만원) 과제유형 품목지정 (과제수) 시장선도를위한한국주도형K-Sensor기술개발 시장주도형K-센서기술개발 시스템 반도체 731 1 신시장창출을위한수요연계 시스템반도체기술개발 신시장창출을위한수요연계 시스템반도체기술개발 시스템 반도체 1,500 1 산업현장맞춤형온디바이스 AI반도체기술개발 산업현장맞춤형온디바이스 AI반도체기술개발 시스템 반도체 4,320 4 화합물전력반도체고도화기술개발 상용화소자 및 모듈 시스템 반도체 5,500 5 반도체첨단패키징 선도기술개발 기술선도형 첨단패키징기술개발 반도체 공정장비 8,775 6 기술자립형 첨단패키징기술개발 반도체 공정장비 6,000 5 글로벌기술확보형 첨단패키징기술개발 반도체 공정장비 3,025 5 민관공동투자반도체 고급인력양성 민관공동투자반도체 고급인력양성 반도체 공정장비 4,597 22 PIM인공지능반도체 핵심기술개발 PIM인공지능반도체 핵심기술개발 반도체 공정장비 2,000 2 합 계 36,448 51 ※ 평가결과에 따라 지원 연구개발과제별 총 연구개발비 및 연구개발 내용 등은 연구개발과제 평가단 심의를 통해 조정될 수 있음 ※ 상기 지원대상 과제 목록과 관련된 사항은 ‘9. 기타유의사항’을 참조 ※ 각 세부사업별 상세 지원대상 사업 및 과제(품목 및 RFP) 목록은 첨부파일(붙임 01. 신규지원 대상 연구개발과제 안내문) 참조 ※ ‘R&D 자율성트랙(舊R&D 샌드박스)’ 과제의 신청자격 및 방법은 다음과 같으며 세부 신청자격, 심의기준 등은 별첨(R&D 자율성트랙 제도 안내) 및「연구자율성 촉진을 위한 특별요령」참고 R&D자율성트랙 신청 □ R&D자율성트랙 ㅇ ‘R&D자율성트랙’이란 우수 R&D 기관에 대해 연구수행 과정의 여러 규제를 대폭 완화해 주는 제도로 연구개발과제 협약 후 주관연구개발기관이 선택적으로 신청할 수 있음 ㅇ ‘R&D자율성트랙’ 유형은 R&D자율성트랙(일반)과 R&D자율성트랙(지정) 2가지가 있으며, 각 유형별 신청자격은 별첨(R&D자율성트랙 제도안내) 참조 ㅇ 위 지원대상 연구개발과제에서 ‘R&D자율성트랙’ 신청유형(일반/지정)은 ‘붙임 01. 신규지원 대상 연구개발과제 안내문’ 참조 ㅇ ‘R&D자율성트랙’ 선정은 신규과제의 연구개발기관이 확정된 이후 별도의 신청과 심의절차를 거쳐 확정되며, 세부 내용은 별첨(R&D자율성트랙 제도 안내) 참조 ㅇ 위 연구개발과제의 신청조건과 ‘R&D자율성트랙’의 신청조건은 별개이고, ‘R&D자율성트랙’은 선택사항이며, ‘R&D자율성트랙’으로 선정되지 않더라도 연구개발과제의 선정 및 수행에는 영향이 없음 4-2. 신청자격 □ 주관연구개발기관 및 공동연구개발기관 ◦기업, 대학, 연구기관, 연구조합, 사업자단체, 의료기관 등 「산업기술혁신촉진법」 제11조 제2항 및 같은 법 시행령 제11조, 「산업기술혁신사업 공통 운영요령」 제2조제1항제3호, 제4호 및 제4의2호, 9의2부터 9의5, 제58호에 해당하는 기관 ◦주관연구개발기관이 기업인 경우는 접수마감일 현재 법인사업자이어야 하며, 선정평가 개최일 이전에 기업부설연구소(한국산업기술진흥협회 인정서 기준)를 보유하고 있어야 함 ※국외기관(기업, 대학 및 연구소 등)의 경우 연구개발기관 또는 연구개발기관 외 기관으로 참여 가능 4-3. 지원제외 처리기준 □ 아래의 경우 지원대상에서 제외 처리되나, 선정평가일의 3영업일 전 18:00까지 공문으로 별첨(사전지원제외 기관 변경 요청서)을 제출하여 연구개발기관 변경 등으로 사전지원제외 사유를 해소할 경우 선정평가에 상정할 수 있음. 단, 주관연구개발기관 및 연구책임자의 변경은 허용되지 않음 ㅇ주관연구개발기관, 공동연구개발기관, 주관연구개발기관의 장, 공동연구개발기관의 장, 연구책임자가 접수 마감일 현재 국가연구개발사업에 참여제한을 받고 있는 경우 ㅇ접수마감일 현재 연구개발기관(단, 비영리기관 및 공기업(공사)은 적용 예외), 연구개발기관의 장(단, 공직자윤리법 제3조의2에 따라 공직유관단체로 지정된 기관은 적용 예외), 연구책임자(공동연구책임자 제외)가 아래 사유에 해당하는 경우 1. 기업의 부도 2. 세무당국에 의하여 국세, 지방세 등의 체납처분을 받은 경우(단, 중소기업진흥공단 및 신용회복위원회(재창업지원위원회)를 통해 재창업자금을 지원받은 경우와 신용보증기금 및 기술신용보증기금으로부터 재도전기업주 재기지원보증을 받은 경우는 예외로 한다) 3. 민사집행법에 기하여 채무불이행자명부에 등재되거나, 은행연합회 등 신용정보집중기관에 채무불이행자로 등록된 경우(단, 중소기업진흥공단 및 신용회복위원회(재창업지원위원회)를 통해 재창업자금을 지원받은 경우와 신용보증기금 및 기술신용보증기금으로부터 재도전기업주 재기지원보증을 받은 경우는 예외로 한다) 4.파산·회생절차·개인회생절차의 개시 신청이 이루어진 경우(단, 법원의 인가를 받은 회생계획 또는 변제계획에 따른 채무변제를 정상적으로 이행하고 있는 경우는 예외로 한다) 5. 최근 3개 회계연도 말 결산 재무제표*상 부채비율이 연속 500% 이상(자본전액잠식이면 부채비율 500% 이상에 포함되는 것으로 간주한다.)인 기업 또는 유동비율이 연속 50% 이하인 기업(단, 기업신용평가등급 중 종합신용등급이 'BBB' 이상인 경우, 기술신용평가기관(TCB)의 기술신용평가 등급이 “BBB” 이상인 경우 또는 외국인투자촉진법에 따른 외국인투자기업 중 외국인투자비율이 50%이상이며, 기업설립일로부터 5년이 경과되지 않은 외국인투자기업인 경우, 또는 산업기술혁신사업 공통운영요령 제2조제9의7호의 산업위기지역 소재 기업은 예외로 한다.) 이때, 사업개시일로부터 접수마감일까지 5년 미만인 기업의 경우는 적용하지 아니한다. - 상기 부채비율 계산시 한국벤처캐피탈협회 회원사 및 중소기업진흥공단 등 「공공기관의 운영에 관한 법률」에 따른 공공기관으로부터 최근 2년 간 대출형 투자유치(CB, BW)를 통한 신규차입금 및 상환전환우선주(RCPS)는 부채총액에서 제외 가능 - 상기의 신용등급 ‘BBB’에는 ‘BBB+’, ‘BBB’, ‘BBB-’를 모두 포함함 - 회계연도 말 결산 이후 재무상황이 호전된 경우, 수정된 재무제표와 외부회계법인의 의견서 제출 가능 - 한국채택국제회계기준(K-IFRS)을 적용함에 따라 부채비율 및 유동비율에 문제가 발생한 경우에는 일반기업회계기준(K-GAAP)을 적용하여 부채비율 및 유동비율 판단 가능. 이 경우, 연구개발기관은 부채비율 및 유동비율 판단을 위해 추가적인 회계기준에 따른 자료를 전문기관에 제출하여야 하며, 한국채택국제회계기준과 일반기업회계기준을 혼용할 수 없음. 6. 최근 회계연도 말 결산 기준 자본전액잠식 - 한국채택국제회계기준(K-IFRS)을 적용함에 따라 자본전액잠식이 발생한 경우에는 일반기업회계기준(K-GAAP)을 적용하여 자본전액잠식 여부 판단 가능. 이 경우, 연구개발기관은 자본잠식 여부 판단을 위해 추가적인 회계기준에 따른 자료를 전문기관에 제출하여야 하며, 한국채택국제회계기준과 일반기업회계기준을 혼용할 수 없음. - 상기 자본전액잠식 계산시 한국벤처캐피탈협회 회원사 및 중소기업진흥공단 등 「공공기관의 운영에 관한 법률」에 따른 공공기관으로부터 최근 5년 간 대출형 투자유치(CB, BW)를 통한 신규차입금 및 상환전환우선주(RCPS)는 자본으로 계산 가능 - 회계연도 말 결산 이후 재무상황이 호전된 경우, 수정된 재무제표와 외부회계법인의 의견서 제출 가능 7.외부감사 기업의 경우 최근 회계년도 말 결산감사 의견이 “의견거절” 또는 “부적정” ※ 상기 5호, 6호 및 7호 결산 재무재표 기준은 종속회사가 있는 기업은 별도 재무제표, 종속회사가 없는 기업은 개별 재무제표를 말함(연결 재무제표 기준 실적 불가) ※ 상기 5호, 6호 및 7호 추가자료 제출 시 가결산 자료는 인정되지 않음 (단, 외부회계법인의 검토의견서가 있는 경우는 예외) ㅇ연구개발과제의 주관연구개발기관인 중소기업 또는 중견기업 중 한계기업이 접수 마감일 기준으로 주관연구개발기관으로 동시에 수행하는 산업통상자원부 소관 연구개발과제수가 아래 표의 기준 초과인 경우에는 사전지원제외로 처리함. 단, 공통운영요령 제20조제3항 각 호 어느 하나에 해당하는 연구개발과제는 연구개발과제 수에 포함하지 않음. 주관연구개발기관 유형(한계기업) 연구개발과제 수 중견기업 4개까지 수행 가능 중소기업 2개까지 수행 가능 * “한계기업”이란 최근 3개 회계연도 말 결산 재무제표**상 이자보상비율이 연속으로 1미만인 기업임. 이때, 기업신용평가등급 중 종합신용등급 또는 기술신용평가기관(TCB)의 기술신용평가 등급이 ‘BBB’ 이상인 한계기업과 사업개시일로부터 접수마감일까지 5년 미만인 한계기업에 대해서는 정상기업 기준을 적용함 ** 종속회사가 있는 기업은 별도 재무제표, 없는 기업은 개별 재무제표를 말함(연결 재무제표 기준 실적 불가) *** 주관연구개발기관으로 신청한 중소기업 또는 중견기업이 정상기업(한계기업이 아닌 경우)이면 산업통상자원부 소관사업의 신청 연구개발과제 수에 제한이 없음 ※ 선정평가 이후 상기 사전지원제외 항목에 해당되는 항목이 확인된 경우, 해당과제의 선정 취소 또는 협약을 해약할 수 있음 □ 다음의 경우는 지원대상에서 제외될 수 있음 ㅇ신청과제가 해당사업의 기본목적에 부합되지 않은 경우 ㅇ신청과제가 접수기간 내 신청 필수서류를 제출하지 아니하였거나, 제출양식을 준수하지 않은 경우 및 전산 업로드가 되어 있지 아니한 경우 ㅇ신청서류가 허위이거나 거짓인 경우 ㅇ신청과제의 기술개발 목표 및 내용이 기지원, 기개발된 과제와 동일한 경우 ㅇ신청과제가 공고된 기술범위에 부합하지 않은 경우 ㅇ주관연구개발기관, 공동연구개발기관, 연구책임자 등이 접수마감일 현재 각종 보고서 제출, 기술료/정산금/환수금/제재부과금 납부 등 의무사항을 불이행하고 있는 경우 ㅇ참여연구원이 국가연구개발사업 참여율 및 참여 과제수 기준을 만족하지 못하는 경우 - 사업을 신청하는 참여연구원의 과제 인건비계상률은 10% 이상이고 동시에 수행하는 국가연구개발사업 과제는 최대 5개 이내여야 하며, 이 중 연구책임자(세부주관책임자 포함)로서 동시에 수행하는 국가연구개발사업 과제는 최대 3개 이내여야 함 - 단, 「공통운영요령」제20조2항 1호부터 4호, 7호에 따른 연평균 연구비 6천만 이하의 소규모 과제, 연구개발과제의 조정 및 관리를 목적으로 하는 연구개발과제([품목번호] 2025-글로벌기술확보형-품목-일반-15) 중 어느 하나에 해당하는 과제는 연구개발과제 수에 포함하지 아니 하나 참여연구자의 인건비계상률에는 포함함 ․참여연구자(연구책임자 및 공동연구개발기관책임자도 포함)의 과제 인건비계상률은 기관 기본사업(연구기관만 해당)에 참여하는 비율을 포함하여 100%를 초과할 수 없으며, 정부출연연구기관, 특정연구기관, 전문생산기술연구소 등 인건비가 100% 확보되지 않는 기관에 소속된 연구원의 총 과제 인건비계상률은 기관 기본사업을 포함하여 130% 이내에서 산정 가능 ◦안전관리형 과제로 지정된 과제가 「공통운영요령」제2조 1항 40의3호에 따라 수립한 안전관리 계획이 미흡한 경우 ㅇ 연구책임자 및 공동연구개발기관책임자의 소속기관이 신청기관과 상이한 경우(단, 소속기관장이 겸임 또는 겸직을 허가한 경우와 산업기술연구조합육성법에 따른 산업기술연구조합이 신청기관인 경우 및 기업에 근무하는 정부출연연구기관의 기업지원연구직은 예외) ㅇ 과제기획 단계에 참여한 실무작업반 전문가(담당PD 포함)가 기획에 참여한 해당 과제에 대하여 참여연구자로 참여하는 경우(붙임 참조) 4-4. 과제 차별성 제기 ◦지원대상 과제가 정부에 의해 기 지원ㆍ기 개발되었거나 민간에 의해 기 개발된 사실을 발견한 경우에는 차별성 미흡을 제기할 수 있음 ※정부에 의한 기 지원ㆍ기 개발 여부 확인 방법 - 한국산업기술기획평가원 소관사업 기 지원과제 자료 : 산업기술 R&D 디지털 플랫폼(srome.keit.re.kr) > 협업 > 과제찾기 - 타기관 공개자료 : 국가과학기술지식정보서비스(www.ntis.go.kr) > 통합검색 > 과제검색 ◦제기기간 : 2025. 1. 17 ~ 2025. 2. 21 ◦제 기 처 : (41069) 대구광역시 동구 첨단로 8길 32(신서동 1152) 한국산업기술기획평가원 미래반도체실(☎ 053-718-8518) ◦제기방법 : 제기기관 대표자 명의의 공문 제출(관련 근거자료 첨부) 5. 평가 절차 및 기준 5-1. 평가절차 □ 평가절차 및 평가일정 공고 (산업부, 1월) → 신청 서류 접수 (주관연구개발기관, 1∼2월) → 사업설명회 (KEIT, ‘25.1.22.) → 사전검토 (KEIT, 2∼3월) 연구개발계획서 평가 및 연구개발비 적정성 검토 (평가위원회, 3∼4월) * 필요시 서면평가 운영 가능 → 신규과제 확정 (산업통상자원부, 사업별심의위원회, 4월) → 평가결과 통보 및 이의신청 (4월) → 협약체결 및 정부지원연구개발비 지급 (4∼5월) ※ 상기 일정 및 평가방식, 평가절차는 내·외부 상황에 따라 변경될 수 있음 ※ 사업별 심의위원회 : 평가결과 조정․심의(사업별 심의위원회 생략될 수 있음) ㅇ 사업설명회 - 일시 및 장소 : 2025. 1. 22(수) 15:00 ∼ 17:00, 대구 무역회관 대회의실 * (주소) 대구광역시 동구 동대구로 489 / KTX동대구역 도보 15분 거리 - 내용 : 신규지원 대상과제 공고 설명 및 질의응답 ㅇ 사전검토 : 전문기관은 신청기관의 연구개발계획서 및 제출서류, 공고 부합성 등을 검토 ◦연구개발계획서 평가 : 평가단은 연구개발계획서를 중심으로 평가를 실시하며, 신청기관은 평가단 질의에 대하여 답변을 제출하여야 함 - 외부 상황에 따라 온라인 형태로 평가를 실시할 수 있음 - 신청기관의 평가위원회 대면 발표 시 경합의 경우에는 과제별 발표 시간 배정은 과제번호가 큰 순서부터 먼저 발표함 ◦연구개발비 적정성 검토 : 연구개발과제별 연구비의 적정성 검토를 통해 연구개발계획서의 구체화 및 내실화 ※ 인건비, 연구장비비, 재료비 등 단가, 소요량의 적정성·필요성 등 검증 강화 ◦이의신청 : 연구개발과제평가단에서 선정방법 및 절차 등 중대한 하자가 있는 경우, 1회에 한하여 신청할 수 있음 5-2. 평가기준 □ 평가항목 ㅇ 연구개발과제 유형에 따라 평가항목을 달리 정함 과제 유형 평가항목 세부 항목 원천기술 기술성(60) ▪목표 및 연구개발의 도전성 및 창의성(50) : 정부지원필요성, RFP/품목 부합성, 목표의 구체성 및 정량 정도, 목표의 수준 및 도전성, 질적 우수 지재권 창출 가능성, 연구개발 내용 및 방법의 창의성 ▪연구방법 및 추진전략 관련 계획의 충실성(10) : 개발 내용 및 방법의 적정성, 연구개발비 규모 및 계상내용의 적정성, 외부기술 도입 적정성 연구역량(20) ▪연구책임자 등 연구조직 역량(20) : 연구책임자의 전문성⋅연구윤리, 참여연구진의 역량/역할의 구성, 연구시설장비 등 연구 인프라, 연구인프라 활용계획 적절성, 지재권 관리인력의 운용 및 관련 지재권 보유정도 사업화 및 경제성(20) ▪사업화 계획 및 의지(5) : 사업화를 위한 투자계획 적정성, 시장분석 및 표준화, 인증 대응 등 사업화 추진전략의 타당성 ▪경제성(15) : 기술개발을 통한 추가적인 가치 창출 가능성(기술이전, 매출, 수익, 수입대체, 수출효과, 고용창출 등) 혁신제품 기술성(40) ▪목표 및 연구개발의 도전성 및 창의성(35) : 정부지원필요성, RFP/품목 부합성, 목표의 구체성 및 정량 정도, 목표의 수준 및 도전성, 질적 우수 지재권 창출 가능성, 연구개발 내용 및 방법의 창의성 ▪연구방법 및 추진전략 관련 계획의 충실성(5) : 개발 내용 및 방법의 적정성, 연구개발비 규모 및 계상내용의 적정성, 외부기술 도입 적정성 연구역량(20) ▪연구책임자 등 연구조직 역량(20) :연구책임자의 전문성⋅연구윤리, 참여연구진의 역량/역할의 구성, 연구시설장비 등 연구 인프라, 연구인프라 활용계획 적절성, 지재권 관리인력의 운용 및 관련 지재권 보유정도 사업화 및 경제성(40) ▪사업화 실적(15) : 연구팀의 과거 사업화 실적 적정성, 과거 관련 기술이전 및 사업화 실적 적적성 ▪사업화 계획 및 의지(10) : 사업화를 위한 투자계획 적정성, 시장분석 및 표준화, 인증 대응 등 사업화 추진전략의 타당성 ▪경제성(15) : 기술개발을 통한 추가적인 가치 창출 가능성(기술이전, 매출, 수익, 수입대체, 수출효과, 고용창출 등) ※ 사회문제해결형 과제의 경우, 사회적 효과를 반영한 과제의 목표 및 성과지표 검토 ㅇ 지원대상 과제 : 신청과제의 평가점수가 70점 이상인 과제는 “지원가능과제”로 하며, 종합평점이 70점 미만인 과제는 “지원제외”로 분류함. 단, 70점 이상인 과제의 경우에도 해당 분야의 예산 범위가 초과한 경우에는 평가점수가 높은 순위에 따라 우선 지원되어 지원 대상에서 제외될 수 있음 - 동일한 최고점을 받은 과제가 발생할 경우 ①사업화 및 경제성, ②기술성, ③감점 항목 순으로 개별 항목 점수가 높은 과제를 우선 선정 - 통합형 : (총괄연구개발과제 평가점수 x 30%) + ((세부연구개발과제별 평가접수 합계 / 총 세부연구개발과제의 수) x 70%)로 종합평점을 계산 ※ (통합형) 총괄연구개발과제 및 세부연구개발과제 중 일부과제가 평가점수에 따라 ‘지원제외’된 경우 평가단 심의를 통해 전체 연구개발과제에 대한 지원대상 여부를 결정할 수 있음 ※ (병렬형) 총괄연구개발과제가 ‘지원제외’ 되거나 세부연구개발과제 중 일부 과제가 ‘지원제외’된 경우 평가단 심의를 통해 전체 연구개발과제가 지원제외 될 수 있음 □ 접수마감일 기준으로 아래에 해당하는 경우 평가 시 감점함 ㅇ 최근 3년 이내에 국가연구개발혁신법 제32조제1항제3호에 따른 사유로 제재처분을 받은 제재대상자(연구개발기관, 연구개발기관의 장, 연구자 등)가 새로운 연구개발과제를 신청하는 경우(3점) ㅇ 최근 3년 이내에 정당한 사유 없이 연구개발과제 수행을 포기한 자(연구개발기관, 연구개발기관의 장, 연구자 등)가 새로운 연구개발과제를 신청하는 경우(3점) * ‘24년 예산 감액으로 인한 중단(포기)과제의 경우 감점 미해당 ㅇ 접수마감일 현재 해당 연구개발기관 또는 소속 연구책임자가 국연법 제32조제1항에 따른 제재부가금 또는 국연법 제32조제3항에 따른 환수금의 전부 또는 일부의 납부 의무를 불이행하고 있는 경우(3점) ※ 최종 점수 산출 시 상기 감점 기준에 따라 감점을 제하되, 총 5점을 초과하여 감점할 수 없음 6. 근거법령 및 규정 □ 근거법령 : 산업기술혁신촉진법 및 동법 시행령, 국가연구개발혁신법 및 동법 시행령 □ 관련규정 ㅇ「산업기술혁신사업 공통 운영요령」, 「기술료 징수 및 관리에 관한 통합요령」, 「산업기술혁신사업 보안관리요령」, 「산업기술혁신사업 연구·윤리 진실성 확보 등에 관한 요령」, 「산업기술개발장비 통합관리 요령」, 「산업기술혁신사업 기술개발 평가관리지침」, 「연구자율성 촉진을 위한 특별요령」 7. 신청방법, 신청서 제출기한 및 접수처 □ 연구책임자가 온라인에 접속하여 접수마감일 18시까지 모든 과제 정보(신청항목)를 전산에 입력하고 제출 대상 서류를 업로드를 완료하여 ‘제출완료’ 상태인 연구개발계획서(과제)만 접수하는 것을 원칙으로 함. 전산 정보 입력 및 서류 업로드 시 최소 1시간 이상 소요될 수 있으며 기간 내에 완료되지 않은 과제에 대한 구제는 절대 불가 (접수 유예 없음). 구분 기간 공고기간 ◦공고기간 : 2025. 1. 17(금) ~ 2. 21(금) 18:00까지 신청서 및 관련 양식 교부 ◦양식교부 : 2025. 1. 27(월) ~ ◦양식교부 및 접수안내 : 범부처통합연구지원시스템(www.iris.go.kr) 접수기간 ◦접수기간 : 2025. 2. 7(금) ~ 2. 21(금) 18:00까지 * 접수마감시간 엄수 요망 (18시 이후 수정 또는 제출 불가) ㅇ 기관·인력 신규가입 등을 위한 법인실명인증, 개인실명확인은 해당 인증기관(서울신용평가정보)의 사무처리 시간(~18:00) 내에만 가능하고 미인증으로 인한 기관·인력의 신규등록 불가 시 온라인접수 진행이 되지 않으므로 유의바람 ㅇ 전산시스템 접수 중 문의사항은 사무처리 시간(~18:00) 내에 범부처통합연구지원시스템 고객센터(☎1877-2041), 산업기술 R&D상담콜센터(☎1544 - 6633)으로 문의 요망 ※ 접수 마감일에는 접속 과부하로 인하여 접수가 지연되거나 장애가 발생할 수 있으므로 사전에 접수 요망. 또한, 접수 마감일 18시 이후 신규접수 및 수정 불가 ※ 제출된 서류 및 연구개발계획서 등이 허위, 위․변조, 그 밖의 방법으로 부정하게 작성된 경우 관련 규정에 의거, 사전지원 제외, 선정 취소 및 협약해약 등 불이익 조치함 ※ 필수서류 미제출·오제출 등 신청기관의 행정착오로 인한 지원제외 등 불이익 조치는 신청기관에 책임이 있으므로 필히 사전에 관련 서류를 확인하여 신청하시기 바람 ※ 접수 시 주관연구개발기관의 연구책임자가 로그인하여 입력·제출이 원칙 ※ 직인이 필요한 별첨 서식의 경우 스캔 업로드를 원칙으로 하나, 일부 온라인에서 자동으로 생성되는 서식의 경우는 전자서명 등으로 대체 가능 ※ 통합형은 총괄연구개발과제 및 세부연구개발과제별로 연구책임자가 각각 온라인제출 ※ 제출된 서류는 일체 반환하지 않음 □ 신청방법 : 연구개발계획서 및 첨부서류 전체 온라인 접수 (오프라인 서류 제출 불필요) □ 연구개발계획서 접수처 ㅇ 범부처통합연구지원시스템(www.iris.go.kr) → 사업정보 > 사업공지 > 사업공고 메뉴(주관연구개발기관이 대표로 온라인제출) ※ 범부처통합연구지원시스템(IRIS) 접수 대상 사업의 경우, 접수 불가시 기존 산업기술 R&D 디지털플랫폼(srome.keit.re.kr)을 활용하여 접수 예정 (추후 별도 공지) 8. 제출 서류 사항 □ 제출된 서류 및 연구개발계획서가 허위, 위․변조, 그 밖의 부정한 방법으로 작성된 경우, 관련 규정에 의거 선정 취소 및 협약 해약 조치함 번호 서 류 명 제출방법(제출형식) 비고 1 연구개발계획서(필수) 온라인 업로드(hwp) - 기본정보에 대한 온라인 전산 입력이 완료되어야 함 - 2 사업자등록증(필수) 온라인 업로드(PDF) - 영리기업만 제출 주관+공동연구개발기관 모두 3 연구개발기관 대표의 참여의사 확인서(필수) 온라인 업로드(PDF) - 모든 신청 연구개발기관이 한 장에 날인 또는 개별 낱장 제출 가능 주관+공동연구개발기관 모두 4 (국외기관용)산업기술혁신사업 참여의사 확인서(비필수) 온라인 업로드(PDF로 스캔) 해당시 제출 5 개인정보 및 과세정보 제공활용동의서(필수) 온라인 업로드(PDF로 스캔) 주관+공동연구개발기관 모두 6 연구윤리·청렴 및 보안서약서(필수) 온라인 업로드(PDF로 스캔) 주관+공동연구개발기관 모두 7 주관연구개발기관의 기업부설연구소 인정서(필수) 온라인 업로드(PDF로 스캔) 주관연구개발기관 8 연구개발기관 책임자의 재직증명서(필수) 온라인 업로드(PDF로 스캔) 주관+공동연구개발기관 모두 9 연구개발기관의 신청자격 적정성 확인서(필수) 온라인 전산 입력(PDF로 스캔) 주관+공동연구개발기관 모두 10 감점사항 확인서(비필수) 온라인 전산 입력(PDF로 스캔) - 증빙서류는 필요시 온라인 업로드(PDF 스캔) 해당시 제출 11 연구수행총량 준수 확약서(비필수) 온라인 업로드(PDF로 스캔) 주관연구개발기관이 한계기업인 경우 제출 12 연구자의 동시수행 과제수 확약서 (필수) 온라인 업로드(PDF로 스캔) 주관+공동연구개발기관 모두 13 수요기업 확약서 (비필수) 온라인 업로드(PDF로 스캔) 해당시 제출 14 비공개과제 신청서 (비필수) 온라인 업로드(PDF로 스캔) 해당시 제출 15 연구개발기관의 회계감사보고서 또는 재무제표* * 종속회사가 있는 기업은 별도 재무제표, 없는 기업은 개별 재무제표를 말함(연결 재무제표 기준 실적 불가) 온라인 재무정보시스템으로 제출 (www.new.findsystem.co.kr 접속 후 한국산업기술기획평가원 선택) - 온라인 재무정보시스템 미활용 기관은 과제접수 기간 종료 후, 전문기관 담당자 안내에 따라 사전검토기간에 업로드 - 표지(회계사 직인 포함), 재무상태표(표준대차대조표), 손익계산서(표준손익계산서)를 PDF로 스캔한 파일 * 국세청에서 발급하는 표준재무제표증명은 회계사 직인 불필요 * 비영리와 상장사(거래소․코스닥) 미제출, 그 외 기업은 제출(직전년도로부터 최근 3년 결산 자료) 영리기관 (주관+공동연구개발기관 모두 별도 사이트 내 재무정보 입력) 16 대학 연구근접지원인력 활용 확약서(비필수) 온라인 업로드(PDF로 스캔) 해당시 제출 ※ 과제참여자 : 연구책임자 및 연구자 모두에 해당 9. 기타 유의 사항 □ 신청 시 유의사항 ㅇ “기술료 징수” 과제는 영리기관이 반드시 연구개발기관으로서 과제에 참여해야 함 ㅇ 융합 R&D : 대내외 환경 변화에 적극적으로 대응할 수 있는 가치창출형(산업고도화, 사회문제해결, 신산업(시장)창출) 연구개발과제 ㅇ 혁신도전형 과제 : 실패가능성은 높으나 성공 시 혁신적 파급효과가 기대되며 세계최초에 도전하거나 완료시점에서 세계최고 수준을 목표로 하여 공고 시 명시한 연구개발과제로서, 공통운영요령 제32조의6(최종평가) 제6항에 따른 우수연구성과 연계지원 가능 과제임 ㅇ IP R&D 연계 : 특허대응전략 수립을 위해 특허청 ‘IP R&D사업’과 연계하는 것을 원칙으로 함(특허전략 수립비를 계상(별도 안내 예정)하여야 하며, 특허전략 수립비는 다른 용도로 전용(변경)이 불가함) ㅇ 표준 연계 : 연구개발계획서 내에 표준화 관련 연구내용과 함께 국제표준화기구(ISO/IEC/JTC1)에 기고발표하는 것을 원칙(표준화 목표수립)으로 하며 상세내용은 표준화 과제별 동향 보고서(별첨) 참고 - 국제표준화기구에서 활동하는 전문가(국제의장단 등)가 참여하거나, 관련 TC의 COSD기관 등의 컨설팅 비용을 산정하여 추진계획에 반영 하여야함 ㅇ 디자인 연계 : 디자인 전문회사 등 전문 기관에 의한 연구개발 세부내용이 연구개발계획서에 포함되어야 함 ㅇ 경쟁형 R&D : 선정평가를 통해 복수의 연구개발기관(n배수)을 선정·지원할 수 있으며, 이 경우 단계평가 등을 통해 계속 수행 1개 과제를 최종 선별함 ㅇ 국제공동 : 국외 소재 기업, 대학, 연구기관 등이 연구개발기관 또는 연구개발기관 외 기관으로 참여 ㅇ 복수형 R&D : 동일 연구개발과제에 복수의 연구개발기관(n배수)이 동시에 수행하는 연구개발과제일 경우 해당 ㅇ 대형통합형 : 산업생태계 육성과 산업 밸류체인 형성을 목적으로 하는 복수의 세부연구개발과제로 구성된 연구개발과제가 해당됨 (5개 이상의 연구개발기관이 참여) ㅇ 서비스형 : 공통운영요령 [별표4] 산업기술혁신사업 인건비 현금 인정 분야 해당 과제 ㅇ 국가핵심기술 : 국내외 시장에서 차지하는 기술적·경제적 가치가 높거나 관련 산업의 성장 잠재력이 높아 해외로 유출될 경우에 국가의 안전 보장 및 국민경제의 발전에 중대한 악영향을 줄 우려가 있는 산업기술 ※ 산업기술혁신사업 보안관리요령 제9조에 따라 보안과제에 해당되므로 보안과제로 체크하여 연구개발계획서를 제출하고, 선정 시 관련 규정을 준수하여야 함 ㅇ 안전관리형 : 연구실, 연구개발 장소 및 외부환경의 안전 확보를 위해 재해유발 위험이 높거나 위험물질을 취급하는 등 사람의 신체, 재산에 피해를 줄 가능성이 있어 연구개발기간 및 연구개발과제 종료 후 일정기간 동안 특별한 점검 및 관리가 필요한 연구개발과제 ㅇ Cascading과제 : 주관기업(최근 3년내 주관기관으로 산업기술 R&D 수행경험이 있는 대기업, 중견기업 및 우수평가를 받은 중소기업에 한함) 단독으로 과제를 신청(컨소시엄을 구성하여 신청 불가)하고, 선정평가시에는 기업역량 및 기술조달(공동연구·외주용역 포함) 계획을 종합적으로 평가하고, 선정된 과제는 협약체결 이후 기업이 주도하여 컨소시엄을 구성하는 방식의 과제 유형임 ㅇ 주관연구개발기관인 중소기업은 사업시작일로부터 2년 내에 특허대응전략을 수립하기 위한 특허전략 수립비를 계상하여야 하며, 선진특허분류(Cooperative Patent Classification)에 따른 선행기술과의 중복 회피전략을 포함해야 함. 특허전략 수립비는 다른 항목으로 전용(변경)이 불가하나 전략수립 완료 후 잔액에 대해서는 연구비 변경 가능. 단, 주관연구개발기관이 자체 특허분석 조직을 보유한 경우에는 미계상 가능 - 중소기업이 주관하는 연구개발과제의 경우 특허청 ‘IP-R&D사업’과의 연계를 위한 비용 사용이 가능함 ㅇ 혁신제품형의 경우, 주관연구개발기관이 중소·중견기업이면서 사업화 컨설팅을 희망하는 경우, 전체 연구개발기간 중 컨설팅을 희망하는 연차에 사업화 컨설팅 비용을 연구활동비에 계상 가능 ㅇ 외부 기술을 도입 후 도입된 기술을 바탕으로 추가 기술을 개발하는 ‘기술도입비’는 현물(기술매매, 기술 라이센싱 비용) 또는 현금으로 산정할 수 있음 - 총 연구개발비의 30% 이내에서 계상 가능하나, 국내에 없는 국외기술 도입시에는 총 연구개발비의 50%까지 계상 가능. 다만, 평가단 심의를 거쳐 상기 기준액을 초과하여 계상 가능 * 현물 : 접수마감일 기준 2년 이내로부터 실제 지급한 도입비의 50% 이내 * 현금 : 목표달성을 위해 연구개발간 중 도입할 기술의 실지급 비용 ㅇ 연구개발 수행에 대한 정보가 NTIS(국가과학기술지식정보서비스)를 통해 공개됨으로 인해 직접적 피해가 우려되는 연구개발과제는 비공개과제 신청서를 제출하여 과제수행정보에 대한 비공개를 요청할 수 있음. 다만, 평가단 심의를 거쳐 비공개과제로 분류되지 않을 수 있으며, 비공개과제로 결정되었더라도 단계평가 시 비공개 지속여부를 별도로 판단함 * NTIS 공개정보 : 참여기관, 참여연구원, 과제명, 연구목표, 연구내용, 기대효과 등 ㅇ 연구개발과제별로 신청 가능한 정부지원연구개발비의 최대범위는 품목별, 과제제안요구서별로 명기된 지원 금액을 초과할 수 없음 ㅇ 3천만원 이상(부가가치세 및 구입·설치등에 필요한 부대비용 포함)의 연구시설·장비를 구매 또는 임차할 경우, 연구개발계획서에 기재 및 ‘연구시설·장비 구입 또는 임차활용계획서’를 제출하여야 함 ㅇ 총괄관리만 수행하는 총괄연구개발과제(통합형/병렬형)의 연구개발기관은 연구수당 산정이 불가함 ㅇ 기타 세부내용은 첨부의 지원대상 사업 및 과제(품목 및 RFP) 목록을 참조 ㅇ 미응모 시 재공고(접수기간 연장)할 수 있음 - 접수결과 미응모인 RFP/품목에 대해서는 동일 RFP/품목으로 재공고 할 수 있음. 이 때, 상세 내용은 연구개발계획서 접수 마감일 이후로부터 2주 내외로 범부처통합연구지원시스템(www.iris.go.kr) 또는 산업기술 R&D 디지털 플랫폼(srome.keit.re.kr)를 통해 재공고하며, 재공고 기간은 15일 이내임 -재공고는 미응모 된 RFP/품목에 대한 접수기한 연장을 의미하며, 재공고 기간 동안 추가 접수되는 과제의 유‧무에 관계 없이, 접수 마감일 이후에는 최초 공고(2025년 1월 17일 공고)와 동일한 평가 항목 및 평가 절차에 따라 평가 진행 ※자세한 사항은 재공고시 세부내용 참조 ㅇ 선정된 과제의 연구개발비(연구비) 및 연구개발기간은 평가결과에 따라 조정될 수 있으며, 과제 추진 중 관련 규정에 따른 평가 등을 통해 과제가 중단될 수 있음 ㅇ 공고된 연구개발과제는 평가결과에 따라 선정되지 않을 수 있음 □ 지식재산권 및 발생품의 귀속 ◦연구개발성과를 연구개발기관이 각자 창출한 경우 해당 연구성과를 창출한 연구개발기관의 소유로 함 - 단, 주관연구개발기관은 국외에 소재한 기관(기관⋅기업⋅단체⋅외국인 등 포함)과 공동으로 연구를 수행하는 경우 국외기관의 연구개발성과를 국내 소재 연구개발기관의 소유로 하거나 국내 소재 연구개발기관이 우선적으로 연구개발성과실시를 할 수 있도록 하여야 함 ◦여러 연구개발기관이 공동으로 연구개발 성과를 창출한 경우 연구개발기관별 기여도를 기준으로 소유비율을 정하는 것을 원칙으로 하되, 연구개발기관 간의 협의에 따라 연구개발성과의 소유비율 및 연구개발성과 실시 등에 관한 사항을 정한 경우 그 협의에 따름 □ 중소기업에 대한 IP 실시권 확산 ◦연구개발기관은 해당 연구개발과제를 통해 각자 개발한 성과물의 실시를 위하여 필요한 범위 내에서 동 과제의 다른 연구개발기관이 보유한 성과물을 실시할 수 있음. 이때, 성과물의 실시기간 및 조건에 대해서는 서로 합의하여 정함 ◦비영리기관은 참여기업 아닌 중소기업이 무형적 성과물에 대해 실시 허락을 요청한 경우 이에 응하여야함 -다만, 중소기업인 실시기업에 대한 기술료율은 「기술료 징수 및 관리에 관한 통합요령」에 따른 기술료율 이내에서 서로 합의하여 정함 ◦기타「산업기술혁신사업 공통 운영요령」제37조(사업 결과의 공개 및 활용 촉진) 및 37조의2(기술실시계약의 체결) 참조 □ 보안등급 분류 ◦신청자는 신청 과제의 보안등급(보안/일반)을 분류하여 이를 연구개발계획서에 표기하여야 함 ◦보안과제는 아래의 어느 하나에 해당하는 연구개발과제임 -세계 초일류 기술제품의 개발과 관련되는 연구개발과제 -외국에서 기술이전을 거부하여 국산화를 추진 중인 기술 또는 미래 핵심기술로서 보호의 필요성이 인정되는 연구개발과제 -「산업기술의 유출방지 및 보호에 관한 법률」제2조제2호의 국가핵심기술과 관련 된 연구개발과제 -「대외무역법」제19조 1항 및 동법 시행령 제32조의2의 수출허가 등의 제한이 필요한 기술과 관련된 연구개발과제 -「방위사업법」 제3조제1호에 따른 방위력개선사업과 관련된 연구개발과제 ㅇ 선정된 연구개발과제 중 외국에 소재한 기관ㆍ단체 또는 외국인과 공동으로 연구를 수행하는 경우에는 해당 연구개발과제가 「대외무역법」 제20조제2항에 따라 전략물자에 해당하는지에 관한 판정을 신청하여 그 결과에 따라 그 연구개발과제를 보안과제로 분류할 수 있음 □ 참여연구자의 최소 인건비계상률 ㅇ 연구책임자를 포함한 모든 참여연구자의 최소 인건비계상률은 10% 이상이어야 함 (단, 학생연구자는 예외로 함) 10. 문의처 □ 상세 RFP/품목 및 관련양식은 IRIS사이트(www.iris.go.kr) 참조 ◦온라인 시스템 접수 및 규정 등 문의 : - 범부처통합연구지원시스템 고객센터(☎ 1877-2041)/ R&D상담콜센터(☎ 1544-6633) ◦선정평가 일정 및 절차, 품목/RFP(기획의도) 문의 분야 선정평가 일정 및 절차 과제 제안요구서(기획의도) 담당부서 연락처 담당부서 연락처 반도체 미래반도체실 053-718-8518 053-718-8582 053-718-8497 시스템반도체 PD 053-718-8415 반도체공정장비PD 053-718-8528

닫기 -

붙임_신규지원 대상 연구개발과제 안내문.hwpx

미리보기

미리보기